赛普拉斯低引脚数HyperRAM™存储器简化嵌入式系统的设计

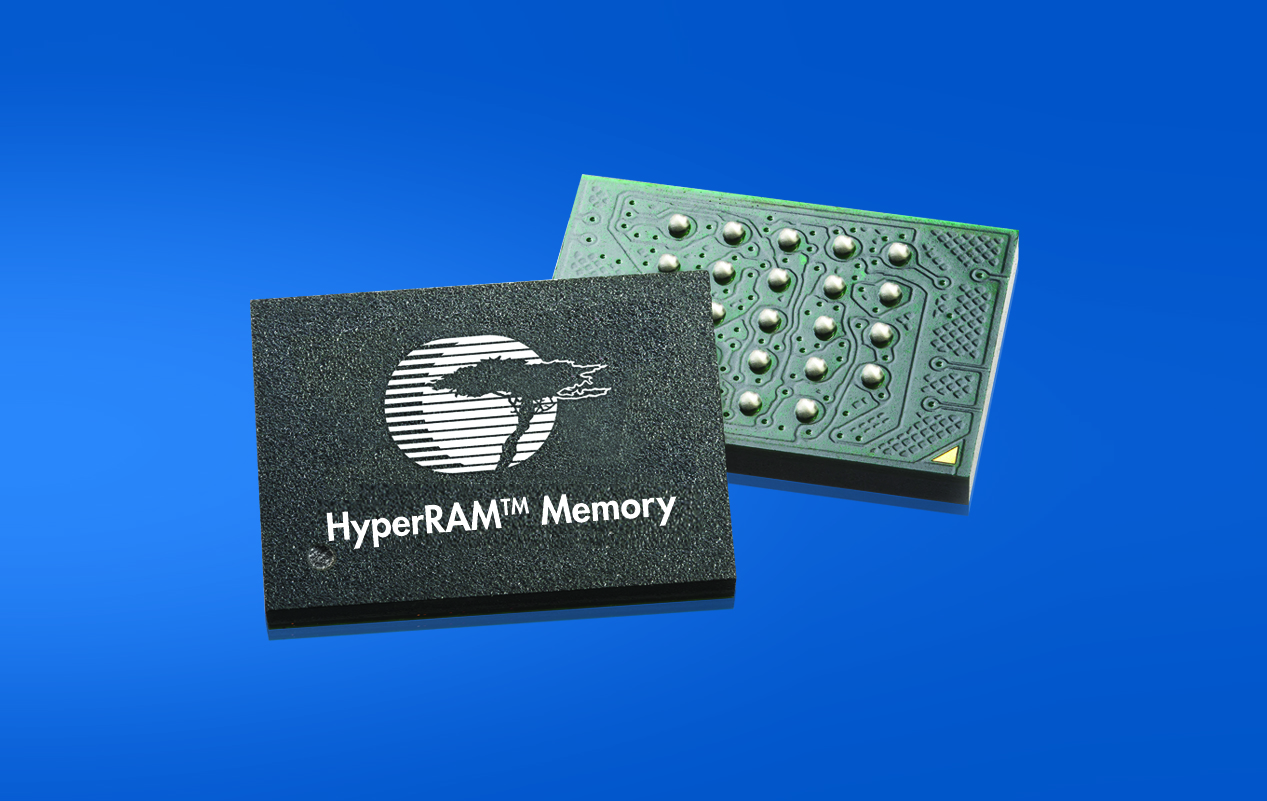

嵌入式系统解决方案领域的领导者赛普拉斯半导体公司今日宣布其基于低引脚数HyperBus™接口的全新高速自刷新动态RAM(DRAM)现开始提供样片。该款64Mb HyperRAM™可用作汽车、工业和消费等各类应用的外置便笺式存储器,用于渲染高分辨率图形或运行数据密集型固件算法。该器件 拥有高达333 MBps的读写带宽,并支持3V和1.8V供电电压。

本文引用地址:https://www.eepw.com.cn/article/201607/293741.htm与赛普拉斯的HyperFlash™ NOR闪存配合使用时,HyperRAM可通过让闪存和RAM共享同一个12引脚HyperBus,为嵌入式系统提供一个简约、经济高效的解决方案。配备SDRAM和Dual-Quad SPI解决方案的传统系统需要使用两条总线上的41个上行引脚来处理数据;HyperRAM与HyperFlash解决方案可将引脚数至少缩减28个,从而简化设计,减低了PCB成本。HyperRAM是汽车仪表盘及信息娱乐系统、通信设备、工业应用和高性能消费电子产品的理想解决方案。有关64Mb HyperRAM的更多信息,敬请访问:http://www.cypress.com/hyperram。

赛普拉斯闪存事业部副总裁Rainer Hoehler表示:“随着高分辨率图形和数据密集型应用在各类系统中日益普及,市场对简约、高性能、可为配备有限板载RAM的控制器提供外置便笺式存储器的DRAM的需求正在不断增长。凭借低引脚数HyperBus接口及其业界领先的读写带宽,我们的全新 64Mb HyperRAM将能满足这一需求。除降低PCB的成本之外,与其他DRAM方案相比,HyperRAM还可通过减少引脚数来降低MCU的成本。”

为加快产品开发速度,赛普拉斯为客户和合作伙伴提供HyperBus主设备接口控制器IP 。该控制器IP可帮助设计人员为其现场可编程门阵列(FPGA)、专用集成电路(ASIC)或专用标准产品(ASSP)主机控制平台添加对HyperBus的支持。该控制器IP支持HyperRAM及HyperFlash产品,而且完全免费和免版税。

供货情况

赛普拉斯64Mb HyperRAM现提供样品,预计将于2016年第三季度量产。该器件将采用24球6x8mm球栅阵列(BGA)封装。

评论