【E课堂】ADC和DAC常用的56个技术术语

本文主要介绍了ADC和DAC常用的56个技术术语,如“采集时间”、“混叠”、“孔径延迟”等,帮助初学者更好的理解专业术语。

本文引用地址:https://www.eepw.com.cn/article/201602/287602.htm采集时间

采集时间是从释放保持状态(由采样-保持输入电路执行)到采样电容电压稳定至新输入值的1 LSB范围之内所需要的时间。采集时间(Tacq)的公式如下:

混叠

根据采样定理,超过奈奎斯特频率的输入信号频率为“混叠”频率。也就是说,这些频率被“折叠”或复制到奈奎斯特频率附近的其它频谱位置。为防止混叠,必须对所有有害信号进行足够的衰减,使得ADC不对其进行数字化。欠采样时,混叠可作为一种有利条件。

孔径延迟

ADC中的孔径延迟(tAD)是从时钟信号的采样沿(下图中为时钟信号的上升沿)到发生采样时之间的时间间隔。当ADC的跟踪-保持切换到保持状态时,进行采样。

孔径抖动

孔径抖动 (tAJ) 是指采样与采样之间孔径延迟的变化,如图所示。典型的ADC孔径抖动值远远小于孔径延迟值。

二进制编码(单极性)

标准二进制是一种常用于单极性信号的编码方法。二进制码(零至满幅)的范围为从全0 (00...000)到全1的正向满幅值(11...111)。中间值由一个1 (MSB)后边跟全0 (10...000)表示。该编码类似于偏移二进制编码,后者支持正和负双极性传递函数。

双极性输入

术语“双极性”表示信号在某个基准电平上、下摆动。单端系统中,输入通常以模拟地为基准,所以双极性信号为在地电平上、下摆动的信号。差分系统中,信号不以地为基准,而是正输入以负输入为参考,双极性信号则指正输入信号能够高于和低于负输入信号。

共模抑制(CMRR)

共模抑制是指器件抑制两路输入的共模信号的能力。共模信号可以是交流或直流信号,或者两者的组合。共模抑制比(CMRR)是指差分信号增益与共模信号增益之比。CMRR通常以分贝(dB)为单位表示。

串扰(Crosstalk)

串扰表示每路模拟输入与其它模拟输入的隔离程度。对于具有多路输入通道的ADC,串扰指从一路模拟输入信号耦合到另一路模拟输入的信号总量,该值通常以分贝(dB)为单位表示;对于具有多路输出通道的DAC,串扰是指一路DAC输出更新时在另一路DAC输出端产生的噪声总量。

微分非线性(DNL)误差

对于ADC,触发任意两个连续输出编码的模拟输入电平之差应为1 LSB (DNL = 0),实际电平差相对于1 LSB的偏差被定义为DNL。对于DAC,DNL误差为连续DAC编码的理想与实测输出响应之差。理想DAC响应的模拟输出值应严格相差一个编码(LSB)(DNL = 0)。(DNL指标大于或等于1LSB保证单调性。)(见“单调”。)

数字馈通

数字馈通是指DAC数字控制信号变化时,在DAC输出端产生的噪声。在下图中,DAC输出端的馈通是串行时钟信号噪声的结果。

动态范围

动态范围定义为器件本底噪声至其规定最大输出电平之间的范围,通常以dB表示。ADC的动态范围为ADC能够分辨的信号幅值范围;如果ADC的动态范围为60dB,则其可分辨的信号幅值为x至1000x。对于通信应用,信号强度变化范围非常大,动态范围非常重要。如果信号太大,则会造成ADC输入过量程;如果信号太小,则会被淹没在转换器的量化噪声中。

有效位数(ENOB)

ENOB表示一个ADC在特定输入频率和采样率下的动态性能。理想ADC的误差仅包含量化噪声。当输入频率升高时,总体噪声(尤其是失真分量)也增大,因此降低ENOB和SINAD(参见“信号与噪声+失真比(SINAD)”)。满幅、正弦输入波形的ENOB由下式计算:

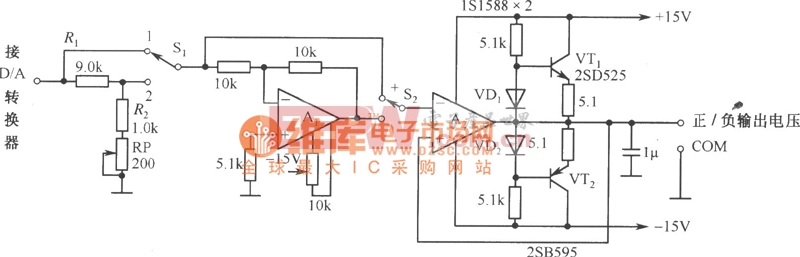

加载-感应输出

一种测量技术,在电路的远端点加载电压(或电流),然后测量(检测)产生的电流(或电压)。例如,带有集成输出放大器的DAC有时就包含加载-感应输出。输出放大器可提供反相输入用于外部连接,反馈通路必须通过外部形成闭环。

全功率带宽(FPBW)

ADC工作时施加的模拟输入信号等于或接近转换器的规定满幅电压。然后将输入频率提高到某个频率,使数字转换结果的幅值降低3dB。该输入频率即为全功率带宽。

满幅(FS)误差

满幅误差为触发跳变至满幅编码的实际值与理想模拟满幅跳变值之差。满幅误差等于“失调误差+增益误差”,如下图所示。

FS增益误差(DAC)

数/模转换器(DAC)的满幅增益误差为实际与理想输出跨距之差。实际跨距为输入设置为全1时与输入设置为全0时的输出之差。所有数据转换器的满幅增益误差都与选择用于测量增益误差的基准有关。

评论