利用USB2.0技术的高速双路数据采集系统

摘要:本文设计了一种基于USB2.0芯片CY7C68013和Maxim公司的高速并行模数转换芯片MAX1195的高速双路数据采集系统,采用EZ-USB FX2 的特有的GPIF(General Programmable Interface)传输方式,彻底打破了8051CPU对USB2.0传输速率的瓶颈,同时避免了使用其他微处理器或者CPLD、FPGA等的硬件开支。本文详细介绍了该数据采集系统的硬件组成和软件设计,包括单片机CY7C68013的固件设计和计算机主机用户程序。通过与高精度激光纵模分析仪的连接调试,证明该系统已经达到了既定目标。

1.引言

近年来,USB接口由于其传输速率高,真正的即插即用等优点正在逐渐取代传统的计算机接口如:RS232,EPP等。目前,许多的芯片生产商都推出了符合USB协议的芯片,如Philips公司的PDIUSBD12,NS公司的USBN9602等。在众多的USB2.0芯片中,Cypress公司的EZ-USB FX2(CY7C68013)芯片是一个不错的选择。本文设计了一种基于EZ-USB FX2和MAX1195的数据采集系统,该系统符合USB2.0协议标准,通过与高精度激光纵模分析仪连接进行调试,证明该系统达到了预定目的。

2. CY7C68013芯片和MAX1195芯片介绍

2.1 CY7C68013介绍:

CY7C68013在一块芯片上同时集成了USB2.0收发器,串行接口引擎SIE,增强型的8051微控制器以及一个可编程外围接口GPIF(General Programmable Interface)。CY7C68013的“量子FIFO”(FIFO,先进先出存储器)特性使得无需8051CPU的任何干预,数据即可从外设上传到主机,这种数据传输模式彻底解决了USB2.0收发器与一般8051微控制器连接时由于8051的时钟频率低而导致的传输速率瓶颈问题。CY7C68013芯片的另一个突出优点是其“‘软’配置”,代码和数据能够直接通过USB接口下载到片内的RAM上,这一功能通过Cypress公司独创的“重枚举”(ReNumerationTM)功能实现。CY7C68013芯片有四个可编程的批量、中断、同步传输端点,可以分别设置为双缓冲,三缓冲和四缓冲模式,8位或者16位的外部数据接口,该接口可以根据需要工作在 GPIF或者SLAVEFIFO模式。其中GPIF能够和绝大部分并行接口如FIFO等实现“无胶”连接,即无需外加任何微控制器或CPLD、FPGA 等。本文的设计中采用了GPIF方式。

2.2 MAX1195介绍:

MAX1195是由MAXIM公司推出的一款低功耗、双路、高速、八位模数转换芯片,采用流水线(Pipeline)结构,最高采样率40Mbps,内部集成了两个 ADC,真正实现两路同步采样转换。其工作电压范围是2.7V-3.6V,具有减小功耗的休眠模式和关断(Shut-Down)模式,单端或者差分输入方式,片上采样保持(T/H)电路,内部或者外部参考电压,含有用户可选择的数据输出格式:二的补码格式或者补偿二进制码格式,具有输出使能控制,可以将输出置为高阻态。此外MAXIM还提供了与MAX1195引脚、封装完全兼容的10位、更高采样率的模数转换芯片,如MAX1197、MAX1198等,因此系统升级非常方便。在本文的工作中,采用了内部参考电压、双路单端模拟输入、补偿二进制码输出格式。

3.系统整体构成及其工作原理介绍:

3.1系统构成:

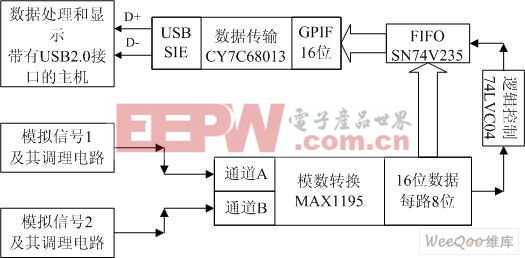

系统的整体框图如图1所示。整个系统主要包括USB传输芯片CY7C68013,先进先出存储器(FIFO)SN74V235和模数转换芯片MAX1195组成。反相器74LVC04主要起MAX1195和FIFO之间的逻辑控制作用。

图1 系统整体框图

3.2系统工作原理:

MAX1195的两路输入信号是同时被采样的,十六位的数据输出总线使两路数据可以同时输出,分别占八位,即:D0A~D7A和D0B~D7B;SN74V235输入为18位,根据CMOS技术的要求,将未使用的D16和D17引脚接地。MAX1195采集到的数据首先送进FIFO里, FIFO的写时钟(WCLK)和AD的转换时钟反相,这样可以充分满足MAX1195输出数据的建立时间,避免发生数据丢失或者数据重复写入现象。 SN74V235的 (Programmable Almost Full)可编程几乎满信号经74LVC04反相后接MAX1195的Sleep和 引脚,以免FIFO发生溢出而丢失数据。SN74V235的数据输出引脚Q0~Q15与CY7C68013的GPIF模式下的数据线FD[15:0]即端口B和端口D组成的十六位数据总线相连,数据SN74V235到EZ-USB FX2的时序过程由CY7C68013的GPIF 控制。FX2采用了“量子FIFO”结构,在FX2里面,数据可以分为两个域:USB域和GPIF接口域。这两个域是独立的,允许分别使用不同的时钟和逻辑控制数据的传输,USB域是由SIE控制的,SIE通过USB口接收或者发送端点FIFO的数据。FX2的“量子FIFO”能够几乎不花时间在这两个数据域中的转移数据,因为这两个域用的FIFO在物理上是同一个。所以根据“量子FIFO”原理,实际上数据已经存在于属于USB域的端点FIFO里面了,采用USB的BULK传输方式,使该数据完全不经过低频CPU干预,而是采用FX2提供的AutoIn模式,即一旦FX2端点缓冲区的数据达到指定字节数,数据将自动被打包从USB口上传到主机。

3.3 GPIF波形及程序介绍:

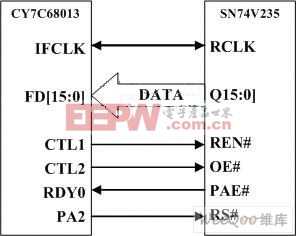

GPIF是FX2的端点FIFO的片内控制器,可以完全代替片外的控制器而实现FX2与外围FIFO的“无胶”连接。GPIF的核心是一个可编程状态机,可以产生六个“控制”(CTL)和九个“地址”(GPIFADR[8:0])信号,可以接收六个外部(RDY)“准备好”输入,八位或者十六位数据总线,时钟可以用FX2的IFCLK,也可以由外围提供。本文GPIF接口的详细硬件连接如图2所示。

图2 GPIF与SN74V235详细连接图

评论