基于ADS8482与TMS320F28335的信号采集系统

摘要:针对加速度计电流信号微弱,给出一种大动态范围的高速高精度信号采集系统。介绍模数转换器ADS8482的性能和工作原理,并给出ADS8482与DSP TMS320F28335的接口设计方案,包括部分硬件电路和软件编程代码。外围扩展的CPLD EPM7128控制ADS8482。该方案实现的加速度计检测装置简单实用,可应用于中低精度的惯性测量中。

关键词:数字信号处理;ADS8482;可编程逻辑;信号采集

惯性测量装置中,加速度计信号的精确检测直接影响到惯性装置的精度,因此提高测量加速度信号精度尤为重要。目前加速度计信号的检测主要采用I/F变换检测技术,测量精度高。但电路复杂,不适合惯性测量装置的小型化,以及中低精度惯性器件的大批量生产。因此,这里提出一种基于A/D转换器ADS8482和TMS320F28335的加速度计信号采集系统设计方案。

1 系统组成及主要器件介绍

图l该信号采集系统的硬件组成框图。采样信号经前级调理电路,以单端输入方式输入至A/D转换器ADS8482进行采集。ADS8482采用18位数据总线输出,直接与TMS320F28335数据线相连,电路的控制部分与引脚电平兼容,是由EPM7128型CPLD实现。采集到的数据通过DSP片上串口输出。

ADS8482型逐次比较A/D转换器输出数据总线方式可配置成8,16和18位。内部提供采样时钟,其采样吞吐率为l MS/s。内部提供4.096 V的参考电压,模拟信号输入,全输入差分范围为±4.096 V。TMS320F28335型单精度浮点DSP主频可达150 MHz,内核电压1.9 V,I/O电压3.3 V;片上带有256 KB的16位Flash和34 KB的16位SARAM,并有128位安全密码钥匙/锁,保护Flash防止固件反向工程。片上通讯端口丰富,集成有3个SCI串口输出通道,并带有16字节的FIFO,2个多通道McBSP串口,2个增强型CAN,1个SPI总线。还带有16通道的12位A/D转换器等资源。

2 系统硬件设计

2.1 前级调理电路

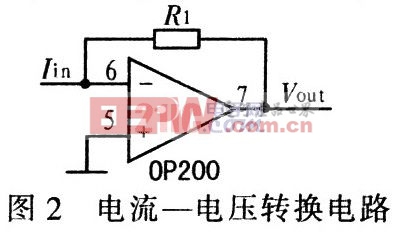

本系统是针对加速度计信号采集而设计的。由于加速度计传感器一般输出的电流信号非常微弱,ADS8482是电压形式的A/D转换器,因此前级电路需设计一个电流转换电压电路。采用运放检测电流有2种方法:一是利用电流在电阻上的压降,再进行电压放大,但该方法所引入的电阻将破坏电路原来的状态,造成测量误差;二是运放的失调电压也被运放放大带入到后级电路。因此这里采用输入电流直接接入运放的反相输入的求和点。如图2所示。

该电路的误差主要来自于运放的输入偏置电流,并和输入电流Iin相叠加引入后级电路。每一级模拟前端电路都会对已处理的信号增加噪声和失真,则直接影响到A/D转换器的精度,因此前级电路的运放选用低噪声,低偏置电压和低偏置电流的OP200配置设计。

评论