用高性能ADC拓展软件定义无线电应用领域

美国国家半导体推出的全新12位模数转换器(ADC)在采样速率、动态性能和集成功能集方面实现了很大的飞跃,其采样速率高达3.6GSPS,同时能将基底噪声保持在-147dBm/Hz。即使是性能最接近的单片竞争产品,也只能实现在1GSPS下12位分辨率的信号采样,这样的性能飞跃究竟是如何实现的?优良的采样速率和噪声特性是如何得到的?使用了哪些基础架构和处理技术?以3.6GSPS速率采样的12位数字数据是如何采样及处理的?需要什么样的时钟电路?本文将就上述问题以及接踵而至的其它诸多问题进行讨论,并将在最后总结可能将受益于该技术的一些应用领域。

本文引用地址:https://www.eepw.com.cn/article/195223.htm千兆采样率级别的ADC设计工程师在系统架构上的选择相对有限,通常快闪式(flash)或折叠式(folding)最为合适。其它诸如流水线(pipeline)架构、分级式(sub-ranging)架构或多步式(multi-step)架构均使用了某种形式的判决反馈回路。例如,在流水线架构中,被采样的模拟信号被低分辨率的ADC转换为数字信号,接着由低分辨率的数模转换器(DAC)还原成模拟信号,这会产生一个误差电压,之后该电压又一次被转换为数字信号,再由控制逻辑进行处理。这一系列连续事件最终限制了流水线架构所能获得的最大采样速率。一些流水线架构的ADC可能同时使用时间交错采样来获得更高的采样速率,但这样的方法在功耗方面的效率相对较低。

尽管由于单次转换仅受限于并行工作的一系列比较器的开关速率,快闪型架构在理论上可实现最快的采样速率,但它同样存在一个重大弊端,即获得N位的分辨率需要2N–1个数据比较器。在分辨率高于8位时,这样做将以巨大的占位面积和更高的功耗为代价。此外,在分辨率为8位或更高时,对如此多的比较器输出信号进行编码也将带来额外的速率限制。基于上述原因,美国国家半导体全新的12位ADC系列使用了折叠式系统架构,并结合了内插技术和对用户透明的片内自校准专利技术。

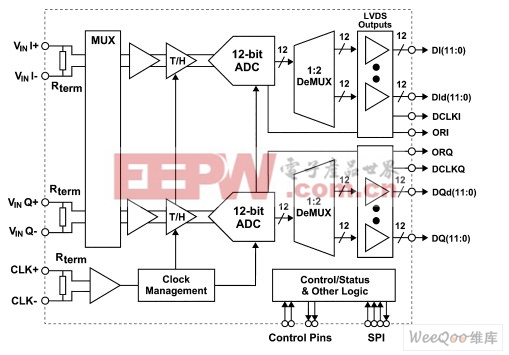

折叠式架构的情况与快闪式基本一致,不同的是比较器可根据折叠阶数进行共享,因此大幅减少了比较器数目。假设折叠阶数为f,则n位转换器所需的比较器数目为2N/f+f–2。内插技术还减少了所需的前端放大器数量,从而使输入信号的负载最小化,进一步降低了功率需求。但折叠式也有一个缺点,与快闪式相比,它更容易受器件偏移的影响。为补偿偏移带来的影响,ADC12D1800采用了专利的片内自校准方案来矫正ADC前置放大电路中的偏移。这将降低折叠式架构产生的积分非线性(INL)误差。与其它系统架构相比,折叠内插式与片内自校准技术的结合大大节省了芯片裸片面积和功耗。上电后自校准在芯片内自动运行,无需任何外部信号或控制电路。该系列ADC采用美国国家半导体自有的0.18μm纯CMOS工艺制造,这种工艺是为获得最大噪声性能同时尽可能降低功耗而专门开发的。其它超高速ADC采用Bipolar(双极)或BiCMOS工艺技术制造,通常需要2个或更多的电源轨且功耗极大。图1中给出了双ADC12D1800的模块图,该芯片运行在1.8V至2.0V的单轨电源下,每个通道的功耗仅为2.05W。

图1:12位模数转换器ADC12D1800模块图。

评论