以1.5 Gbps运行的PRBS发生器

PRBS(伪随机二进制序列)或PN(伪噪声)发生器在数字数据传输中有广泛的应用(参考文献1)。这些电路通常由带反馈的简单移位寄存器构成,它可以用作串行数据链路的测试源。正如它们名称所示,输出序列并非真正随机,实际上是在2N-1位后重复,其中N表示移位寄存器的长度。多项式标注的阶数对应于移位寄存器的长度,因此PRBS的周期就为描述序列提供了一个简便的方法。

本文引用地址:https://www.eepw.com.cn/article/194127.htm

通信设备的测试要使用某种标准多项式。例如,x7+x6+1产生一个 127位的PRBS周期,而x23+x18+1 则产生大于800万位的周期,x31+x28+1产生的周期更长,256倍。有较长周期的 PRBS 通常提供更多的数据类型,从而能更仔细地检测传输系统的性能。

一个采用中间级反馈的简单移位寄存器就可以产生一个PRBS。构成寄存器的触发器运行速度必须与传输速度一致,如果你打算建立一个运行在千兆赫兹时钟速率下的长周期PRBS发生器,则可能产生问题。德州仪器公司的高速串行器TLK2201B运行在高达1.6 Gbps速率下,它提供了一个可能的解决方法。但是,该串行器并不能以原有的全部串行格式接受PRBS,而一次只能接收10位部分。

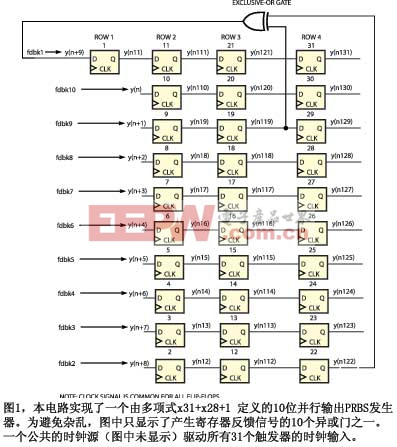

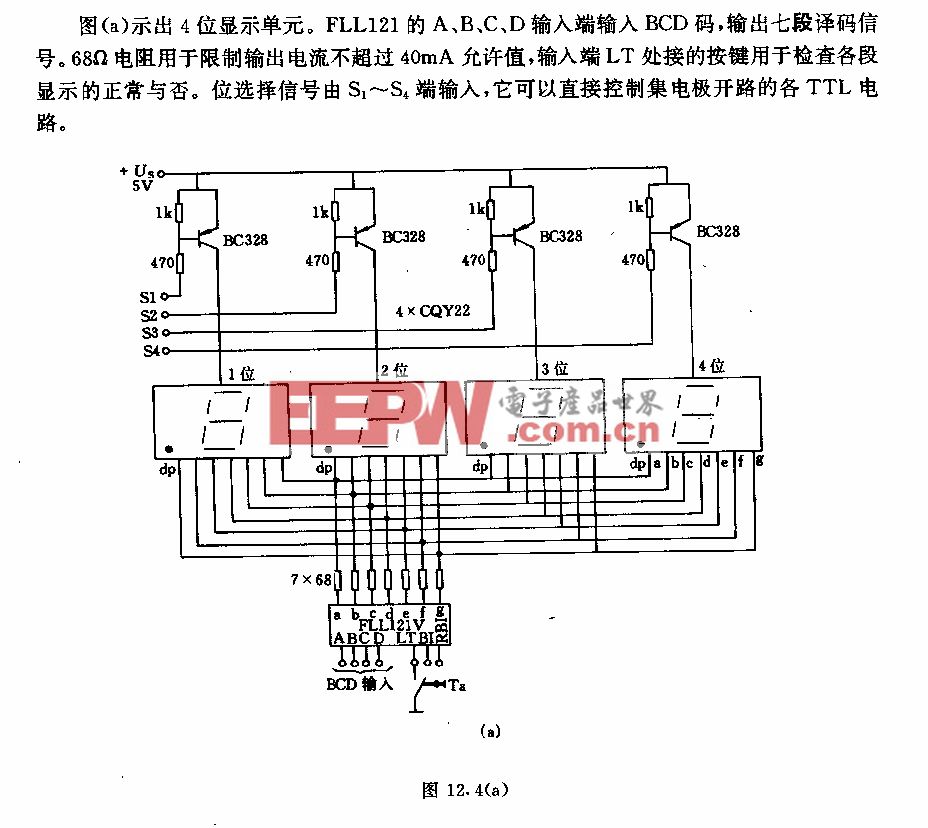

图1中电路表示一个31阶的并行 PRBS 发生器,它提供10位输出段,可以很容易适应其它的PRBS序列和输出宽度。在设计电路时,先画一个有31个触发器的图,每行包含10个触发器。在此例中,设计包含四行,第一行只有一个触发器。图1显示了触发器和编号约定之间的时序关系。

组成的结构形成一个并行移位寄存器,其中第3行直接送至第 4 行,第2行送至第3行,等等。第2行的触发器10至触发器2和第1行的触发器1从反馈路径接受它们的输入。这种排列可保证相连行中的触发器提供10倍于当时间隔的输出,因而发生器的时钟速度为等效串行移位寄存器PRBS实现速度的十分之一。

为确定反馈信号,推导出描述一个标准(即串行)PRBS 发生器输出的公式,对多项式 x31+x28+1,得出 y(n)=y(n-31) xor y(n-28)。用此公式可以推导出描述反馈信号fdbk1 ~ fdbk10的公式。即:fdbk1:y (n+9)=y(n-22) xor y(n-19),fdbk2:y(n+8)=y(n-23) xor y(n-20),... fdbk10:y(n)=y(n-31) xor y(n-28)。例如,反馈信号 fdbk1 来自触发器22和19输出驱动的两个输入异或门的输出。

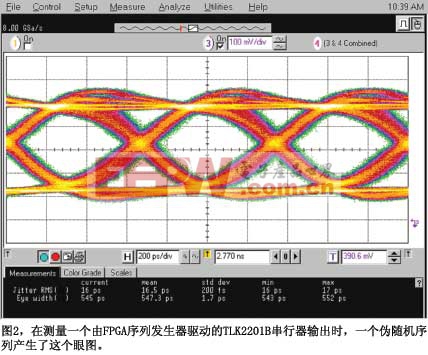

图1电路是用CPLD或FPGA器件实现的VHDL代码。15行~18 行定义了并行移位寄存器,21行~23行定义了反馈电路的结构。本设计实例的电路适合于Xilinx的XC3S50 Spartan 3器件,它运行在150 MHz 时钟速率下;也可以通过一个10位接口,以150 MHz驱动一个德州仪器公司的 TLK2201B串行器。Xilinx's ISE 7.1i 软件编译电路的VHDL文件。图2显示串行器输出的眼图,并确保电路工作在1.5 Gbps。编译软件预测电路应工作在300 MHz以上时钟速率下,但TLK2201B的极限工作频率为150 MHz。

参考文献

1, Miller, Andy, and Mike Gulotta, PN generators using the SRL macro, Application Note APP211, Xilinx Inc, June 15, 2004.

评论