采用HyperLynx解决高速采集板中阻抗匹配的问题

本次设计中高速数据采集板的技术指标如下:a)垂直分辨率12bit;b)双通道同时工作交替采样,单通道采样率为500MSPS;c)有效分辨率位数大于等于10bits;d)信噪比SNR>62dB。该采集板系统的主要器件有ADC芯片,时钟芯片和通道上的模拟放大器和滤波器。

本文引用地址:https://www.eepw.com.cn/article/193441.htm通过对性能指标的综合分析,我们选择ADS5463为我们的ADC芯片,AD9517-3为时钟芯片。数据采集板中遇到的阻抗匹配问题主要集中在这两个芯片上。

ADS5463的采样率为500MSPS,垂直分辨率为12bits,有效分辨位数为10.5bits。ADS5463的时钟信号输入幅值范围很宽,输入的时钟信号峰峰值最大可达到3伏。ADS5463的信噪比和时钟信号的幅度、共模电压的大小、温度以及供电电压的纹波等因素有关。其中时钟信号的幅度对信噪比影响较大,时钟信号的峰峰值越高信噪比越高。数据输出的格式为LVDS电平。

AD9517为可编程的12通道的时钟产生器。AD9517内置有2GHz的VCO,可产生最高800MHz的LVDS时钟信号以及1.6GHz的LVPECL时钟信号。通过对寄存器的设置可以产生不同电平标准以及不同频率的时钟输出信号。

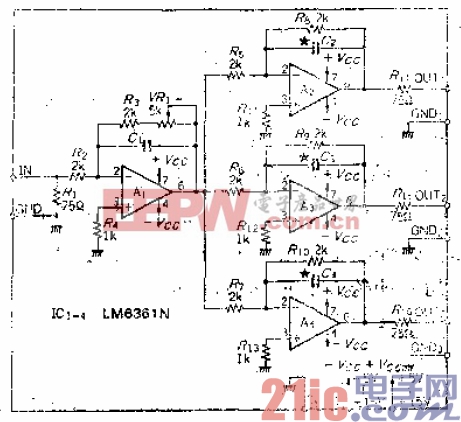

为了尽量增大ADS5463的信噪比,AD9517的输出时钟采用LVPECL电平。LVPECL的信号摆幅为800mV,输出阻抗很低,因此它有很强的驱动能力。ADS5463的输出为LVDS电平、AD9517的输出为LVPECL电平,二者均为差分信号。为了控制差分线的阻抗并且找到一个良好的端接方案,下面引出差分阻抗的定义。

差分线的阻抗

对于FR4材料的边缘耦合微带线,差分阻抗近似为:

式中,Zdiff表示差分阻抗,单位为Ω;Z0表示未耦合时的单端特性阻抗;s表示信号线边沿的间距,单位是mil;h表示信号线与返回路径平面间的介质厚度;FR4介质的介电常数决定了式中的两个系数0.48、0.96。

对于FR4材料的边缘耦合带状线,差分阻抗近似为:

式中,FR4介质的介电常数决定了式中的两个系数0.37、2.9,b表示平面间总的介质厚度,其余同公式(1)。

传输线中,导线引起的总衰减为:

式中,Len表示传输线的长度,单位为in;Z0表示传输线的特征阻抗,单位为Ω;w表示线宽,单位为mil;f表示正弦波频率分量,单位为GHz;Acond表示导线引起的总的衰减,单位是dB;36这个参数和FR4介质的介质耗散因子tan(δ)有关,FR4的介质耗散因子tan(δ)为0.02。

评论