多通道数据采集系统设计

2.5 DSP硬件电路设计

在数据采集过程中,采集的数据缓存在FPGA内部构建的FIFO中在线采集时,通过FPGA与DSP接口将FIFO中的数据转存到DSP外挂的SRAM内,当需要分析数据时再从存储器中取出。DSP外挂Flash存放程序及配置信息。

3 软件设计

3.1 FPGA软件设计

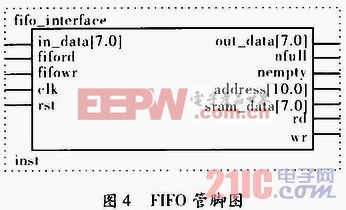

数据在传入FPGA后,直接采用数据在传入FPGA后,可利用SRAM来设计的同步FIFO来缓存采样数据如图4所示:将FIFO抽象为环形数组,并用读或写指针来控制对环形数组的读写。该FIFO提供读使能fiford和写使能fifowr输入控制信号,并指示FIFO的状态非空nempty,非满nfull。未完成一次读写操作地址加1。随着地址的增加,采样数据被依次存入双口SRAM中,当存完数据后向DSP发出信号。本文引用地址:http://www.eepw.com.cn/article/193418.htm

ADC接口模块主要由分频器、通道选择模块及ADC控制模块组成。分频器一方面产牛ADC控制模块的工作时钟,另一方面提供采集启动信号以触发通道选择模块。通道选择控制模块,输出地址信号到多路开关,用来选择采集对应通道的数据信息。该模块由分频器产生的采集信号触发启动。ADC控制模块,主要完成模数转换器的配置与渎取。根据通道选择模块发出的A/D启动信号,按照配置信息对选择的通道进行A/D转换。该模块的数据接收触发信号在一次A/D转换结束后该信号有效,表示开始接收转换结果。为提高准确性,采取平均值滤波的方法,随后将结果输出至寄存器阵列,同时向通道选择模块输出数据有效信号,表示该通道数据采集结束数据有效。

3.2 DSP软件设计

DSP软件设计包括模块化编程,其中包括初始化模块、数据采集模块、通讯模块、FFT功能模块等。

初始化模块涉及锁相环的初始化,Flash的初始化、SRAM的初始化等一锁相环的初始化,系统中PLL输入时钟为50 MHz的晶振,输出时钟为两个,一是DSP内部时SYSCLK1二是EMIF3。为得到这两个时钟而进行初始化。Flash的初始化,EMIF接口对于异步器件的控制通过A1CR来实现,主要根据Flash参数设置数据位宽、读写建立时间、读写选通时间以及读写保持时间。SRAM的初始化,即完成对EMIF内部关于SRAM参数寄存器的初始化。

DSP对数据采集控制主要通过查询与中断两种方式进行。该系统是通过巾断方式进行,即指当FIFO满时产生一个高电平中断。其主要流程由系统初始化和开启中断组成。

初始化程序完成对所有变量及DSP相应寄存器的初始化工作,同时复位SRAM,并完成采集通道及量程的设置,随后开启中断,进入等待中断状态。当检测到中断时进入中断服务程序,并查询FPGA相关寄存器确定是哪一通道的中断,并将数据存于SRAM中。

UART在FPGA内部实现,但接收数据的是DSP。DSP接收数据时UART采用中断方式,即由UART接收FIFO满产生中断通知DSP读取信息。

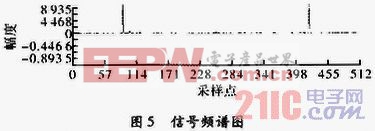

DSP对采集到的数据进行滤波处理、变换、谱分析,下面以FFT为例对信号进行谱分析。FFT算法基本可分为两大类时域捕取法FFT和频域抽取法FFT。在设计中选择简单实用的时域抽取基二FFT算法。并采用基二的突发输入输出结构。如图5为采样信号经过采样点为512的信号频谱图。

3.3 FPGA与DSP的接口设计

FPGA与DSP两者之间的通信,可分为DSP到FPCA为写操作,FPGA到DSP为读操作。DSP发给FPGA的配置信息为通道切换电路的选通信号,各通道数据采集使能信号及清零信号,UART的数据格式及中断源设置等。FPGA返回给DSP的信息主要有数据采集存储的窄满标志,实际采集的数据,UART的中断信息等。

4 结束语

提出了一种基于FPGA+DSP的高速多通道数据采集系统设计方案,将FPGA及DSP的优势充分结合,并针对间歇性数据传输特征,设计以FIFO作数据过渡。该系统经过测试,工作稳定,满足采集速度及A/D转换精度的要求。

评论