一种X波段低相噪跳频源的设计

(6)体积小:24引脚4×4mm SMT封装。

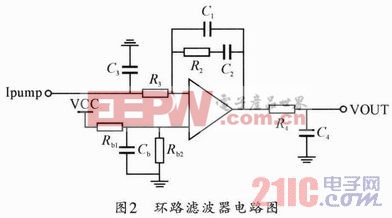

3.2 环路滤波器的设计

环路滤波器设计是锁相环设计的关键部分。环路滤波器处于鉴相器和VCO之间,可以滤除来自晶振的噪声,鉴相器本身的输出噪声和载频分量,滤除杂散,还可以滤除来自VCO的噪声,但最重要的是建立起环路的动态特性。

滤波器设计时带宽需要折中考虑。带宽小,呵降低近端相噪,环路锁定时间长。带宽大,环路锁定时间短,但会引入参考杂散。本设计借助于Hittite PLL Design设计滤波器。该软件是Hittite公司推出的锁相环辅助设计软件,可以仿真锁相环的相噪特性、环路特性等。可通过修改环路带宽、相位裕量、零极点等来修改各参数值。本系统采用四阶有源滤波器。电路如图2所示。本文引用地址:http://www.eepw.com.cn/article/193338.htm

其中Cb=100 nF;Rb1=Rb2=1 kΩ;C1=150 pF;C2=3.3 nF,R2=510 Ω,C3=68 pF;R3=510 Ω,C4=15 pF;R4=1.5 kΩ。此时的环路带宽280 kHz,相位裕度为60°。

3.3 电路设计与软件实现

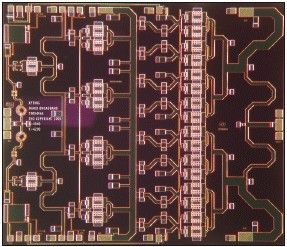

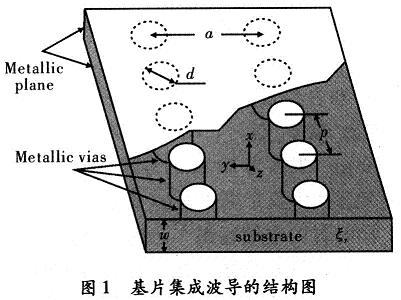

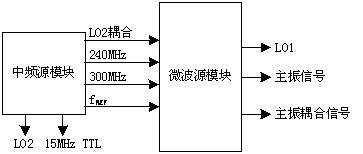

本跳频源输出X波段频率,电路基板采用ROGERS 4350B (介电常数3.48,厚度0.508 mm),各部分电路必须具有良好隔离和屏蔽。整个电路放在铝腔体中,以保证内部和外部的电磁隔离。腔体分为上下两层。锁相环电路放在上层。电源板和控制电路放在下层。为了获得好的相噪指标,对系统的供电设计要特别注意。系统供电包括+15V、+5 V和+3.3 V。+15 V、+5 V由电源板经过滤波后直接给锁相环电路供电。+3.3 V由+5 V经LDO产生。各+5 V电源之间用磁珠进行隔离,各+3.3 V电源间也果用磁珠进行隔离。

HMC704寄存器较多,配置起来比较复杂,是设计难点之一。我们采用Altera公司的FPCAEP1C3T14417对HMC704进行配置。通过SPI串口用开放模式配置,可以减少配置时间,进一步减小跳频时间。利用SCLK上升沿将数据、寄存器地址、芯片地址码依次通过SDI送给PLL内部的移位寄存器后,令SEN变为高电平将移位寄存器中的数据所存至相应锁存器中,锁相环进入相应频率锁定过程。跳频时,改变频点只用改变N整数寄存器和N小数寄存器即可。

4 测试结果与结论

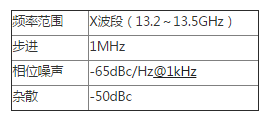

采用Agilent频谱仪N9030A和信号源分析仪E5052B分别对该跳频源的杂散、相噪和跳频时间进行测试。相位噪声测试曲线如图3所示,测试频率为10.47 GHz,相噪指标为-96dBc/Hz@1kHz;杂散测试如图4、图5所示,测试频率为10.44 GHz,图4为近端杂散、图5为远端杂散。杂散优于-70dBc。跳频时间测试的是9.9 GHz到10.93 GHz的跳频时间,约为36 μs。

该跳频源高于指标要求,体积为60x40×19mm3,且性能稳定可靠。该设计方案可应用于同类型的频率频率源设计。

评论