DDS技术在高频石英晶体测试系统中的应用

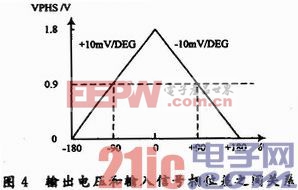

当被测晶体放入π网络电路后,在不同的扫频信号作用下,π网络两端输入和输出信号的相位差不同。π网络两端的输入信号和输出信号分别送入鉴相电路,在鉴相电路的输出端得到与π网络两端输入和输出信号的相位差成正比的电压信号。鉴相电路的输出电压信号和输入信号相位差之间的关系如图4所示。本文引用地址:http://www.eepw.com.cn/article/192856.htm

鉴相电路的输出电压信号经过信号调理电路转变为适合于进行ADC采集的信号。信号通过STM32F103内置的12位ADC通道采集到处理器内部。测量过程时,DDS输出信号的频率由小变大,π网络两端输入信号和输出信号的相位差绝对值由大变小并逐渐接近于零,之后又由小变大。而ADC采集的结果则由小变大,到达最大值后,又由大变小。因此,这个最大值1.8 V处对应的DDS输出信号频率即为石英晶体的串联谐振频率。

2 DDS技术在测试系统中的应用

2.1 DDS技术

DDS有2个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的范围宽,频率分辨率高。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和频率快速转换等优点,广泛应用于电子仪器仪表领域。

AD9912是ADI公司于2007年新推出的一款DDS芯片,内部时钟速度可高达1 GSPS,并集成了14位数模转换器,因此可以直接输出400 MHz信号。AD9912采用48位频率控制字,输出频率分辨率小于4μHz。AD9912兼容多种系统时钟输入方式,石英晶体、晶体振荡器和外部时钟都可以作为其系统时钟输入。由于具有片上系统时钟锁相环(PLL),允许系统时钟输入低至25 MHz。

2.2 信号源硬件设计

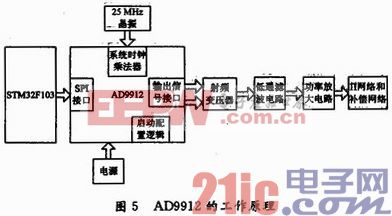

笔者选择ADI公司的AD9912作为信号源的核心。STM32F103通过内置高速SPI总线控制AD9912输出0~400 MHz的扫频信号。AD9912的工作原理如图5所示。

AD9912的外围电路主要由5大模块组成:电源、时钟源、SPI通信接口、启动配置逻辑、输出信号处理电路。

AD9912的电源分为模拟3.3 V、数字3.3 V、模拟1.8 V和数字1.8 V四大类。模拟3.3 V和数字3.3 V经过滤波器互相隔离。模拟1.8 V和数字1.8 V经过滤波器互相隔离。AD9912的参考时钟选用25 MHz的高性能恒温石英晶体,AD9912内部的PLL电路对该参考时钟进行40倍倍频得到1 000 MHz时钟信号作为AD9912的系统时钟。32管脚CLKMODESEL为时钟模式选择管脚,如果使用石英晶体作为系统时钟输入,该管脚应该接地,如果使用振荡器或者外部时钟源作为系统时钟输入,该管脚应被上拉至1.8 V。由于选用的是石英晶体,该管脚接地。

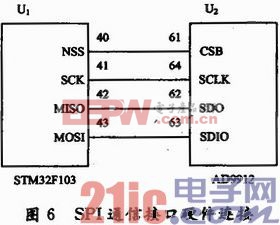

SPI通信接口硬件连接如图6所示。

启动配置逻辑包含S1,S2,S3,S4四个管脚。其中S4为逻辑0时,选择时钟模式:使用石英晶体作为系统时钟输入,并且由AD9912内部的PLL电路进行倍频得到时钟信号;S4为逻辑1时,选择时钟模式:由外部直接输入时钟信号。因此,把S4设置为逻辑0。S1、S2和S3的8种不同逻辑组合,用来选择8组预置的16位频率控制字。允许在未配置I/O寄存器的情况下,产生8种频率不同的信号。由于本测试系统需要的是扫描信号,不需要某固定频率的信号,因此,把S1,S2和S3设置为逻辑0,使DDS在启动时不输出信号。

评论