一种基于FPGA并行流水线的FIR滤波器设计方案

1 Fir滤波器原理

有限冲激响应(FIR)数字滤波器和无限冲激响应(IIR)数字滤波器广泛应用于数字信号处理系统中。IIR数字滤波器方便简单,但它相位的非线性,要求采用全通网络进行相位校正,且稳定性难以保障。FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视。FIR数字滤波器是一个线性时不变系统(LTI),N阶因果有限冲激响应滤波器可以用传输函数H(z)来描述,

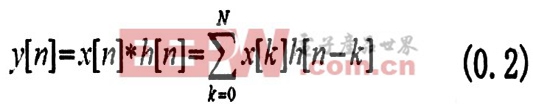

在时域中,上述有限冲激响应滤波器的输入输出关系如下:

其中,x[n]和y[n]分别是输入和输出序列。

N阶有限冲激响应滤波器要用N+1个系数描述,通常要用N+1个乘法器和N个两输入加法器来实现。乘法器的系数正好是传递函数的系数,因此这种结构称为直接型结构,可通过式(1.2)来实现

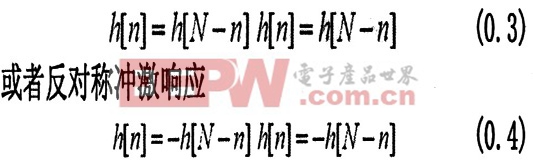

当冲击响应满足下列条件时,FIR滤波器具有对称结构,为线性相位滤波器:

这种对称性,可使得乘法器数量减半:对n价滤波器,当n为偶数时,乘法器的个数为n/2个;当n为奇数时,乘法器的个数为(n+1)/2个。在电路实现中,乘法器占用的逻辑单元数较多。乘法器的增加,意味着电路成本增加,另外对电路的工作速度也有影响。

N阶线性相位的因果FIR系统的单位冲激响应滤波器可用对称冲激响应

来描述。

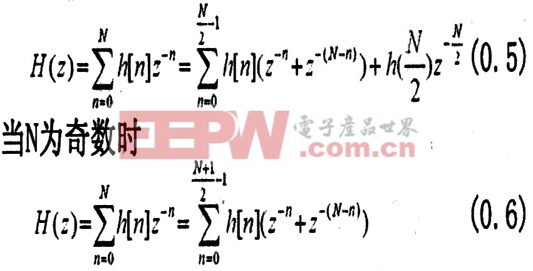

具有对称冲激响应的FIR传输函数的冲激响应可写成如下形式:

当N为偶数时

则FIR线性相位系统的结构可转化成如图1(a)和图1(b)所示。

2 滤波器设计方案、

随着数字技术日益广泛的应用,以现场可编程门阵列(FPGA)为代表的ASIC器件得到了迅速普及和发展,器件集成度和速度都在高速增长。FPGA既具有门阵列的高逻辑密度和高可靠性,又具有可编码逻辑器件的用户可编程特性,可以减少系统设计和维护的风险,降低产品成本,缩短设计周期。

分布式算法是―种以实现乘加运算为目的的运算方法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序不同。简单地说,分布式算法在完成乘加功能时是通过将各输入数据每一对应位产生的部分积预先进相加形成相应部分积,然后在对各部门积进行累加形成最终结果,而传统算法是等到所有乘积产生之后再进行相加来完成乘加运算的。与传统算法相比,分布式算法可极大地减少硬件电路规模,很容易实现流水线处理,提高电路的执行速度。

评论