基于FPGA的VGA图象信号发生器设计

1、引言

本文引用地址:http://www.eepw.com.cn/article/191981.htmVGA(视频图形阵列)作为一种标准的显示接口在视频和计算机领域得到了广泛的应用。VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

VGA图像信号发生器的设计涉及到图像数据的处理,对电路的工作速度和性能要求较高,VGA工业标准要求的时钟频率高达25MHz,使用传统的电子电路设计方法是难以实现的。采用专用的视频处理芯片,其设计技术难度大、开发成本高。本文采用FPGA+MCU方案,利用了Cyclone系列的FPGA高达上百兆的工作频率特性为图像数据处理提供了良好的实时性,其内部集成的数字锁相环为系统的工作时钟提供的良好的稳定性,其内部嵌入的存储器可以存储一定容量的图像信息,丰富的I/O资源可以随即扩展外接大容量存储器的特性,因此由 FPGA完成对图像数据的处理及产生行场扫描时序信号。很好地实现了图象数据处理的实时性和稳定性,达到了性能与价格的完美统一。此外,FPGA的电路可重构性,为系统功能更改和升级以及功能扩展提供了很大的设计空间。由微控制器完成功能设置与控制,如键盘扫描,模式选择与显示控制等。

2、系统的工作原理和组成框图

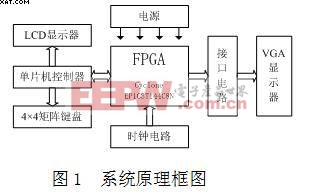

FPGA是整个系统的核心,通过对其编程可输出RGB三基色信号和HS 、VS行场扫描同步信号。当 FPGA接受单片机输出的控制信号后,内部的数据选择器模块根据控制信号选通相应的图像生成模块,输出图像信号,与行场扫描时序信号一起通过15针D型接口电路送入VGA显示器,在VGA显示器上便可以看到对应的彩色图像。FPGA所需的工作时钟由外部高精度有源晶振提供;单片机控制器分析键盘扫描结果,控制液晶显示模块显示相应的功能,由LCD显示输出图象和按键控制模式,并送出相应控制信号给FPGA,系统原理框图如图1。

3、VGA显示器原理

工业标准的VGA显示模式为:640×468×16色×60Hz。常见的彩色显示器,一般由CRT (阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。扫描从屏幕的左上方开始,由左至右,由上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置,在回扫期间,CRT对电子束进行消隐,每行结束是用行同步信号HS进行行同步;扫描完所有行,再由场同步信号VS进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。行同步信号HS 和场同步信号VS是两个重要的信号。显示过程中,HS 和VS的极性可正可负,显示器内可自动转换为正极性逻辑。

行同步信号HS和场同步信号VS的时序图如图2所示, T1为行同步消隐(约为6μs);T2为行显示时间(约为26μs);T3为场同步消隐(两个行周期);T4为场显示时间(480个行周期)。

行同步信号HS和场同步信号VS与图象信号R、G、B的时序关系如图3所示。

对于VGA 显示器的上述五个信号的时序驱动要严格遵循“VGA工业标准”,即640×480×60HZ模式,否则无法显示正确地图象。

VGA工业标准要求的频率:

时钟频率:25.175MHz(像素输出的频率)

行频: 31469Hz

场频: 59.94Hz(每秒图像刷新频率)

图象信号显示的颜色种类与表示R、G、B三基色的二进制数位数有关,表1列出了8种颜色的编码方式。

4、系统设计

4.1 图像信号产生模块的设计

产生图像信号的核心器件采用Altera公司的Cyclone FPGA芯片EP1C3T144C8N。它具有多达20060个逻辑单元。最大用户I/O数 104个。器件中M4K存储块提供288kbit存储容量,能够被配置来支持多种操作模式,包括RAM、ROM、FIFO及单口和双口模式。

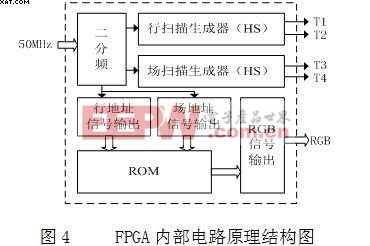

Cyclone器件具有高级外部存储器接口,允许设计者将外部单数据率(SDR)SDRAM,双数据率(DDR)、SDRAM和 DDR FCRAM 器件集成到复杂系统设计中,而不会降低数据访问的性能。并且还具有两个可编程锁相环(PLL)和八个全局时钟线,能提供时钟管理和频率合成,实现最大的系统功能。根据VGA显示原理,图象信号产生器的主要功能是:产生时序驱动信号HS、VS及VGA彩色图象编码信号,同时在正确的时序控制下,输出ROM中的象素数据至显示器的VGA接口,进行图象显示。FPGA内部电路原理结构如图4。本文利用Altera公司QuartusⅡ6.0开发平台,遵循自顶向下的设计方法,针对各功能模块,采用VHDL语言对FPGA器件编程,产生HS和VS扫描时序信号及各种图象信号。

VGA时序信号是图象显示的关键,行场扫描时序的产生,是利用逻辑编程的方法实现的,即用VHDL编写分频器,计时器模块,来获得T1、T2、T3、T4时序。当输出数字、彩条信号和棋盘格图象时,由外部12M有源晶振提供时钟输入,其中行频HS:12MHZ ÷13÷29=31830Hz、场频VS:31830Hz÷480×0.93=61.67Hz、T1=1/31830Hz×4/29=25.96us、T2=1/31830Hz×5/29=6.04us、T3为两个行周期(T1+T2),T4为480个行周期。

图象信号包括数字、彩条、棋盘格,和ROM中定制的图形等。数字信号和彩条信号的产生是按行场方向将屏幕各进行8等分,相当于一个8×8的点阵,在对应位置显示相应颜色即可获得所需图像信号;棋盘格信号是将横彩条和竖彩条相异或获得。ROM中定制的较为复杂的彩色图像,需采用像素点输出,即将图像各像素点的信息存储于ROM中,再以一定的频率输出。FPGA器件ROM的定制有两种方法:第一种方法是利用FPGA器件的嵌入式存储器定制LPM_ROM,用.MIF文件或.HEX文件对其进行初始化,这种方法获得的ROM最大寻址空间为2 12,可以存储一幅分辨率为64×64的图像信息;第二种方法是在FPGA逻辑资源的限度内用VHDL语言定制一个ROM,采用CASE语句对其进行初始化,这种方法获得的ROM在存储深度较大时,编译时对时间的开销较大。ROM初始化完成后,在25MHz的时钟频率下输出存储的图像信息。其图象颜色种类的多少取决于存储空间的大小。

评论