基于FPGA的AES算法芯片设计实现

其中Round1-Round3、FinalRound是由组合逻辑完成的操作,都能够在一个时钟周期内执行完成。这种风格的代码在生成流水线电路时,还需要控制指令的配合。

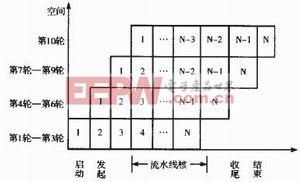

图3是拆分轮运算的流水线时空图。图中数字表示数据分组的序号,整个流水线操作由启动、发起、流水线核、收尾和结束5部分组成,当进入流水线核时的效率是最高的。

图3 拆分轮运算的流水线时空图

用加速比(Speedup)可以衡量采用流水结构之后加密过程相对于非流水结构速度的提高。计算流水线加速比的基本公式为![]() 。

。

设加密N个分组,10轮运算每轮的运算时间为!,则

![]()

当N的取值无限增大时,这个比值将接近于3.33…。因而使用流水结构数据处理速度比非流水结构提高到3倍多。

仿真实验和结果

图4为加密过程时序。针对128bit明文分组和128bit初始密钥的AES算法,在QuartusII软件下,采用中间相遇的设计方法将顶层模块化图形设计与底层VHDL语言描述相结合实现。实验时选用APEX20KE系列的EP20K1500EFC33-3为目标芯片进行仿真和功能验证。密钥装载完毕之后每加密输出一个分组需3个时钟周期,吞吐率为689.500Mbits/s。使用了3056个LUTs,81626个Memorybits,可以满足SDH标准速率STM-4规定的622.080Mbits/s的要求。

|

图4 加密过程时序

结合FPGA的结构特点,本设计实现的IP核具有如下特点:接口设计灵活,外部接口的设计和定义可以根据不同加密芯片的接口设计要求现场改动。资源占用小,脱密电路采用与加密电路部分复用的结构实现,从而节省了资源。设计支持重用,在算法实现顶层设计时采用了模块化设计方法,结构清晰,可以根据不同的功能需求进行改动,利于设计重用

评论