可实现快速锁定的FPGA片内延时锁相环设计

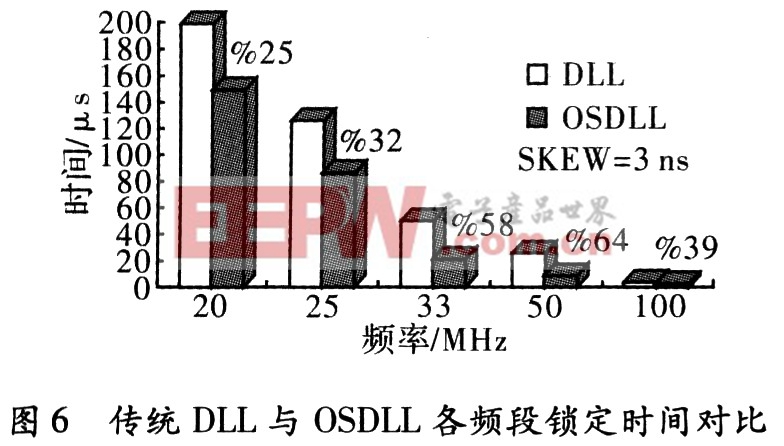

针对这一问题,采用one-shot延时计算机制,即完成SHIFT阶段后首先利用主延时链来计算反馈时OSDLL的特点是复用传统DLL的延时链,one-shot译码逻辑相对简单,没有过多地增加硬件开销,同时保持原DLL架构的优点,在多频段都能够提高锁定速度,频率适应性强。与传统DLL的锁定时间比较,如图6所示。图6中纵坐标代表锁定时间,横坐标代表仿真频率,百分数表示锁定时间相差的比钟上升沿和输入时钟上升沿之间的相位差值(假设有效沿是上升沿),这个延时值以延时单元的数目来表征。将计算后的结果作为SYN逻辑中的可逆计数器0的初值,如图2所示,经过译码后使得主延时链具有一个合理的延时初值。然后DLL进入SYN阶段,按照上述的过程进行同步调整。由于大部分的相差在one-shot计算结果付给可逆计数器时已经消失,DLL只需经过很短的调整周期即可达到同步。这种结构的DLL,称之为OSDLL。本文引用地址:http://www.eepw.com.cn/article/191707.htm

|

|

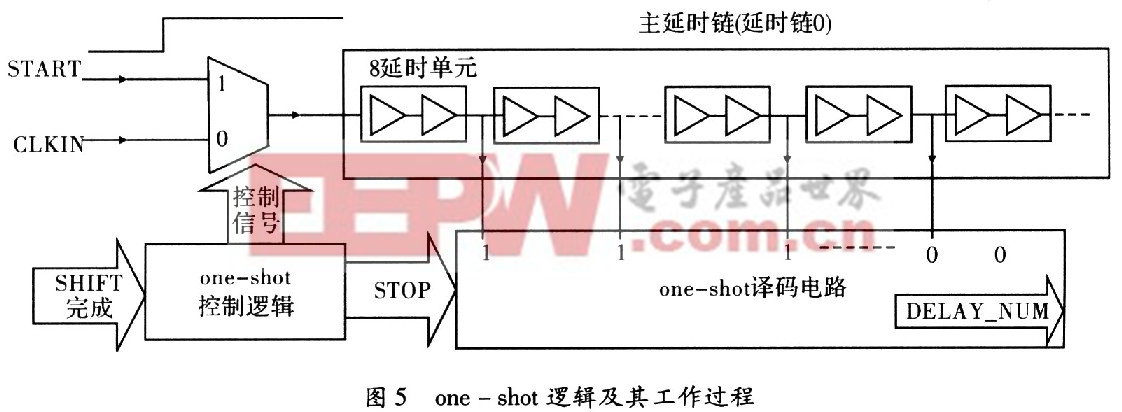

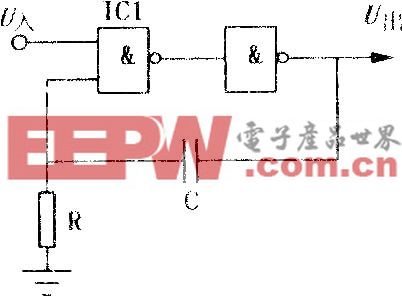

本设计进行one-shot计算时复用主延时链,如图5为one-shot结构,SHIFT阶段完成后在one-shot控制逻辑的控制下首先将图中的开关转向1。主延时链取8个延时单元为一个one-shot延时计算单元,这样可以简化译码电路的规模,同时可以计算出一个合理的延时粗略值,达到硬件增加和功能实现的折中。one-shot工作时首先对主延时链进行复位。然后发出START信号,START信号上升沿同CLKFB同步,STOP信号上升沿同CLKIN同步,START(上升沿后为恒“1”)信号送入延时链的输入端,每个延时计算单元的输出端作为译码器的译码输入,STOP为译码器的采样信号。由于延时单元具有一定的延时值所以,STOP信号有效时,译码电路将采集到“11110…000”的一串译码输入值。通过译码电路计算出其中“l”的个数,从而计算出两时钟沿之间的延时单元数目。将计算好的延时单元数目DELAY_NUM送入数字控制模块的可逆计数器0,如图2所示。开关转向0,CLKIN输入至延时链,启动SYN阶段,开始工作。例,可见在各个频率段,OSDLL都能够明显的降低锁定时间。

基于SMIC O.25 μm工艺,设计OSDLL测试芯片。OSDLL的工作频率在20~200 MHz之间,工作电压为2.5 V。图7为版图,图8为版图后仿真结果。

3 结束语

介绍了DLL架构和工作原理,并基于原DLL结构,加入快速锁定one-shot模块。新的DLL结构OSDLL在提高DLL锁定速度的基础上,没有过多的增加硬件资源,保持了原DLL的时钟综合能力和抗抖动功能。在SMIC 0.25μm工艺下,设计完成OSDLL测试芯片,其工作频率在20~200 MHz之间,锁定时间比传统架构大幅降低。OSDLL架构集成于FPGA芯片内,可有效地优化设计时序,加强系统性能。

fpga相关文章:fpga是什么

鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论