可实现快速锁定的FPGA片内延时锁相环设计

1.2 DLL工作原理

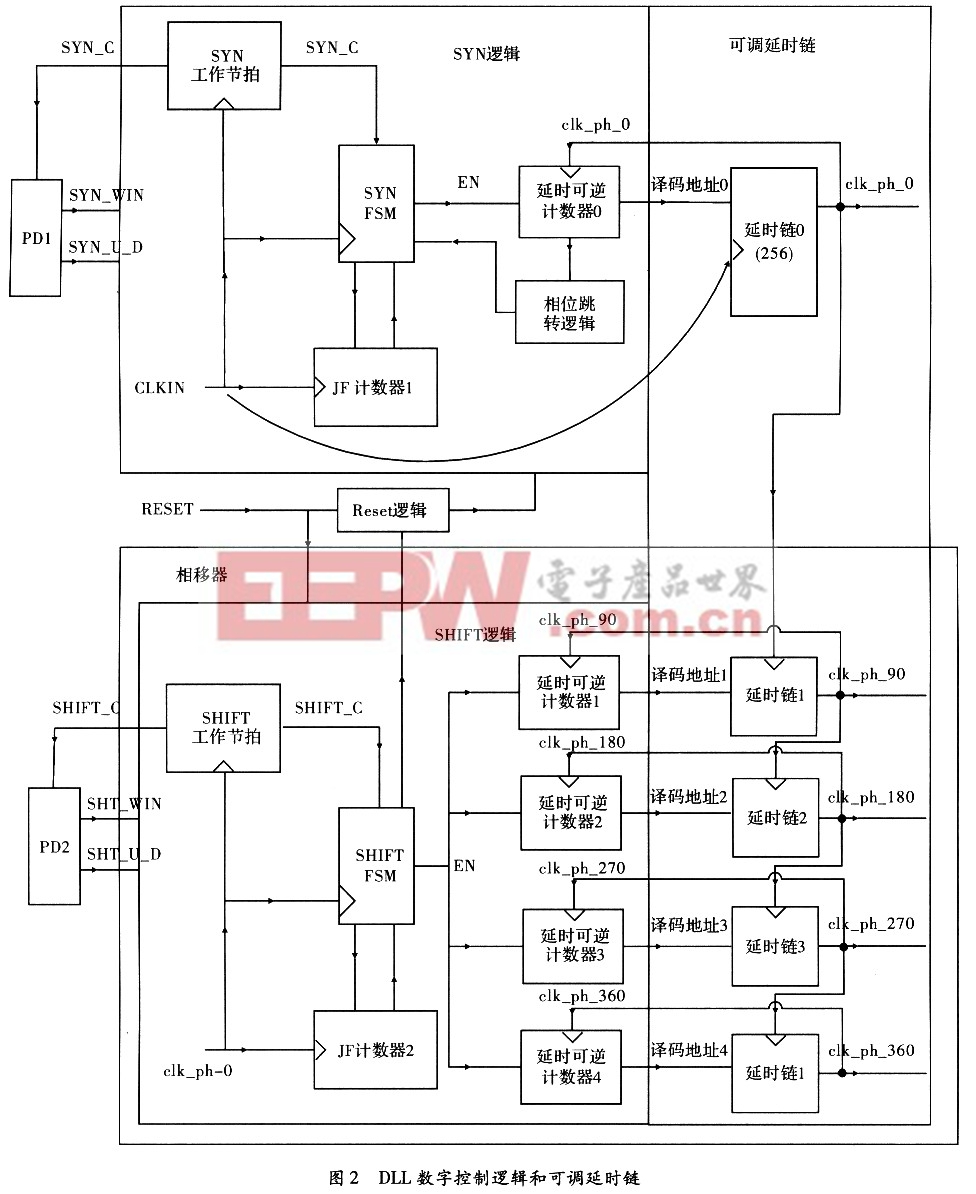

DLL的工作过程依赖于控制逻辑的设计。DLL的控制逻辑主要包括SHIFT控制逻辑和SYN控制逻辑两部分,如图2所示。DLL的工作过程首先进行SHIFT阶段,之后进行SYN阶段。本文引用地址:http://www.eepw.com.cn/article/191707.htm

从图2可见,可调延时链共5条,即一条主可调延时链(延时链0,256个延时单元),4条子可调延时链(延时链1~4,各128个延时单元)。如图2所示,4条子延时链,SHIFT逻辑和一个鉴相器(PD2)构成相移器。SHIFT阶段,相移器工作。相移器采集第一级子延时链的输入时钟clk_ph_0和最后一级延时链的输出时钟clk_ph_360,根据鉴相结果同步调整4条子可调延时链的延时,直至clk_ph_O和clk_ph_360同步。经过相移器的时钟延时是一个周期,从而使得时钟经过相移器中的每个子延时链的输出时钟相移90°,对应图2中分别为clk_ph_O,clk_ph_90,clk_ph_180,clk_ph_270,clk_ph_360。这些相移的时钟可以根据实际的需要由时钟生成模块产生所需要分频(CLKDV),倍频(CIK2X)或移相时钟作为输出时钟,关于分频和倍频电路,如文献。SYN逻辑用于控制将反馈时钟和输入时钟调整至同步。

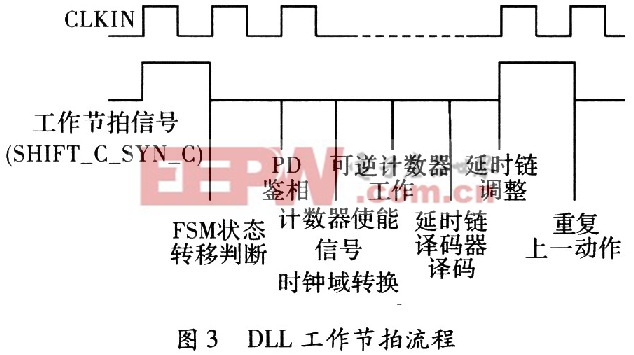

整个SHIFT阶段和SYN阶段都是在各自的控制逻辑模块控制下工作的,以一定的工作节拍实施调整,如图3所示。

图2中工作节拍模块生成工作节拍信号(SHIFT_C,SYN_C)。在工作节拍下,状态机处于某一状态,则根据状态的调整要求依次进行如下操作:鉴相,判断出输入时钟和反馈时钟的相位关系为超前或滞后(SHT_U_D)或SYN_U_D),同时还可以指示两时钟是否进入锁定窗(SHT_WIN,SYN_WIN),如图l所示。鉴相器将这些信息送入控制逻辑模块,在SHIFT阶段,4条延时链对应各自的可逆计数器,负责控制延时链加减延时单元,各计数器工作在自己的时钟域中,如图2所示。根据鉴相的结果和所处的状态机状态,计数器进行计数,计数结果作为延时链的译码地址,最后延时链经过地址译码增加/减少一个延时单元,完成一次工作节拍调节,继而继续进行下一次调整,直到状态机进入锁定状态为止。SYN阶段工作方式类似,但只对主延时链进行调整。实现DLL锁定,同步建立需满足公式,如式(1)所示。

DSYN+SKEW=mult(P) (1)

式中,DSYN为主延时链可以提供的延时;SKEW为时钟偏斜;muh(P)为整数个输入时钟周期。

1.3 抗抖动设计

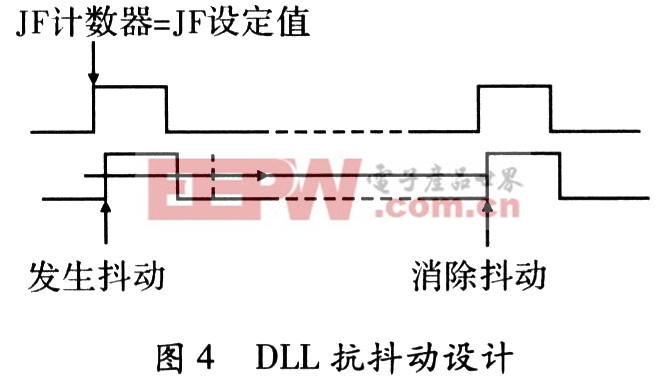

如图2所示,控制逻辑中JF counter1和JF counter2功能模块。用户可以设置抗抖动数值d1,d2,如图1所示,从而对这两个模块中的计数器设定一个计数周期。在DLL锁定之后这两个模块开始工作,按照计数设定值的周期性对锁定后的时钟进行检测。即在计数器达到设定值时,对锁定后的反馈时钟和输入时钟进行鉴相,判断相位关系,控制可逆计数器对锁定后的时钟进行周期性微调干预。如图4所示,在系统内存在干扰时,会产生时钟抖动,若抗抖动模块工作检测到反馈时钟超前于输入时钟,则进行一次微调,消除抖动的影响。抗抖动设计有助于减少抖动的影响。同时由于计数周期可设,使得用户可以在不同系统工作环境下,采用不同的抗抖动设定值,以达到最优的防抖效果。

2 OSDLL架构设计

以上介绍的是传统DLL架构下的设计,其具有设计周期相对较短、工艺可移植、抗干扰能力强等特点。由于其控制逻辑的工作特点,从复位状态开始,延时链复位至O,即可逆计数器从0开始计数。DLL按照工作节拍信号,一拍一拍地进行调整(假设6周期一节拍),当输入时钟频率较低或者时钟相差较大时,其锁定时间将大大增加。取任何固定值作为延时链的复位值,同样存在某一频率段锁定时间较长的问题。

fpga相关文章:fpga是什么

鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论