基于FPGA的PPM调制解调系统设计

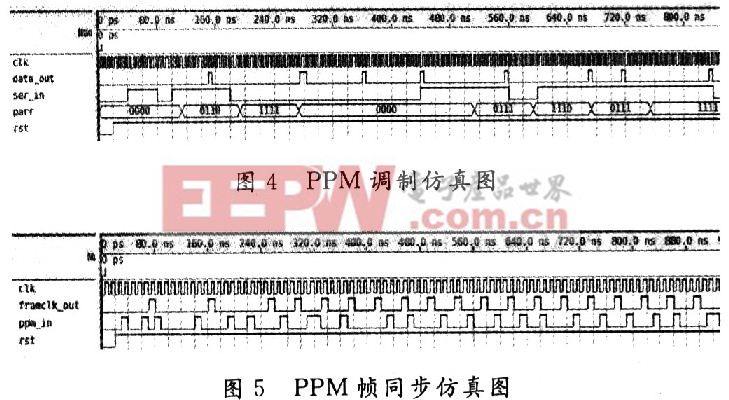

整个系统在Quartus 8.0平台进行仿真,图4为PPM调制仿真图。ser_in为串行输入的数据,parr为串/并转换后的并行数据,data_out即为PPM调制后的输出信号,从图中可以看到PPM调制正确。为了更好地展现程序逐渐同步的原理,选择从4-PPM信号中恢复帧同步,如图5所示,从仿真中,不难看出帧同步输出framclk_out逐渐同步的过程。本文引用地址:http://www.eepw.com.cn/article/191649.htm

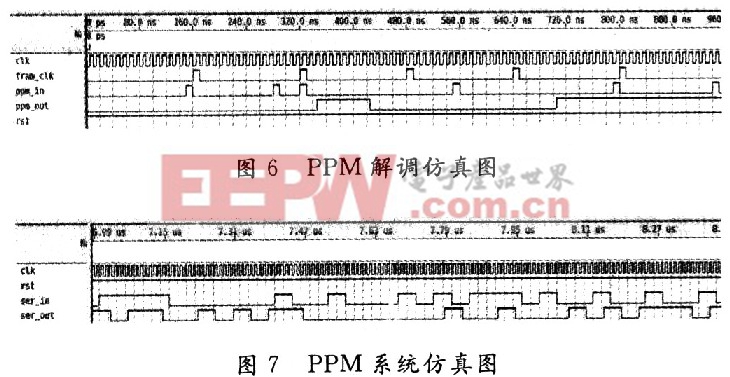

图6为PPM解调仿真图,图7为系统整体仿真,即串行输入数据经PPM调制后,解调程序从已调信号中提取帧同步,并解调出原有串行输入数据,从图7中看到串行输入数据与串行输出数据之间存在一定的延迟,一方面是因为硬件系统自身存在延迟,更主要的原因是由于在PPM调制时,比较器需等待第一次串/并转换完成再进行比较,并输出PPM信号,而解调是在基于调制后PPM信号进行的,从而导致了仿真中的延迟,但在实际运用中这个延迟并不存在。

5 结语

用Verilog HDL语言设计完成了基于FPGA的PPM调制解调系统,并在Quartus 8平台上对调制过程、帧同步过程和解调过程以及整个系统进行功能仿真和时序仿真,从仿真中可以看出整个系统达到了预期的目标,能够高效稳定地完成PPM调制与解调过程,为将来的实用化打下了基础。但另一方面,也在仿真中发现帧同步时间偏长,需要进一步改进。

评论