基于多相滤波的数字接收机的FPGA实现

摘要:给出了一种基于多相滤波的数字信道化接收机的实现方法,系统的处理带宽为875 MHz,解决了高速ADC与FPGA处理速度之间的矛盾。为了克服信道化接收机的接收盲区,采用信道重叠的方法,连续覆盖瞬时带宽。在信道化处理后接测频模块,可以消除虚假信号的输出和提高测频精度。整个接收机在单片FPGA中实现,能够检测同时到达的两个信号,并实时输出脉冲描述字(PDW),经FPGA时序仿真结果验证了算法模型的正确性和有效性。

关键词:数字信道化接收机;多相滤波;参数估计;FPGA

0 引言

信道化接收机是在并行多通道接收机基础上提出的全概率频分信道化接收机,它克服了多部接收机并行工作、多通道下变频等方案具有的设备复杂,各通道性能不一致和可靠性差的缺点。数字信道化接收机具备大的瞬时带宽、较高的灵敏度、大的动态范围,能够检测和处理同时到达的信号、准确的参数测量能力和一定的信号识别能力。直接信道化接收机的运算量大且输出速率与采样速率相同,实现困难,后续处理的压力很大,高速ADC与慢速信号处理器(FPGA,DSP)是一个“瓶颈”;基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在一片FPGA中实现数字信道化成为可能。本文利用信道频率重叠的方法连续覆盖整个瞬时带宽,然后利用Rife算法测频,根据信道重叠的特点,消除虚假信号。系统带宽为875 MHz(62.5~937.5 MHz),可以处理两个同时到达的信号,并实时给出PDW。

1 宽带数字接收机的结构

1.1 数字信道化原理

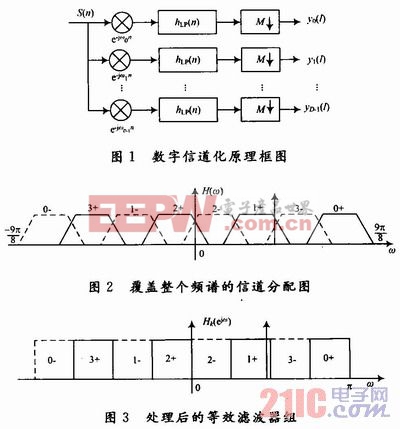

信道划分的基本思想是把信号按频率均匀地分成D个子频段(即信道),每个信道的中心频率为ωk,然后分别移到零中频,再通过低通滤波器滤出。由于子信道的带宽远小于系统瞬时带宽,因此可以采用抽取的方法来降低信号的输出速率,降低后续处理的压力。图1中,hLP(n)为低通滤波器;M↓表示对经过低通滤波器的信号M倍抽取。对于实信号而言,在侦察接收机中,各信道输出经过M=D倍抽取后,会产生频谱混叠,如图2所示。各个信道的中心频率为 ,覆盖整个频域范围。但是这种接收机存在信道的虚假输出。由图2中可以看出,当输入信号位于某一信道时,靠近这一信道的相邻信道会产生虚假输出。图2中实线表示实信道,虚线表示镜像信道。在信道化接收机的输出端接瞬时测频模块,可以消除虚假信号,同时还能提高频率精度。推导计算出混叠部分频率的点数,在固定的某一信道,将重叠部分的点只取一次,删除多余的点数,即消除虚假信号,得到如图3所示的等效滤波器组。

1.2 实信号无盲区信道化接收机数学模型

由图1可得第k路信号的输出为:

评论