基于PCI9054的数据转换模块设计

信号线连接主要包括:LHOLD(申请使用本地总线,输出信号)、LHOLDA(对LHOLD应答,输入信号)、ADS#(新的总线访问有效地址的开始,在总线访问first clock设置时输出信号)、BLAST#(表示为总线访问的last transfer,输出信号)、LW/R#(高电平表示读操作,低电平表示写操作,输出信号)、LA[31:2](地址线)、LD[31:0](数据线)、READY#(表示总线上读数据有效或写数据完成,用以连接PCI9054等待状态产生器,输入信号)。

2.1.3 PCI9054与EEPROM接口

PCI9054在加电启动时,需要从外部EEPROM读取初始化数据来配置PCI9054的内部寄存器,而且依赖于硬件板卡的硬件资源要求,以及选择正确的PCI9054工作模式。PCI9054提供4个管脚与串行EEPROM相连接,它们分别是EEDI、EEDO、EESK和EECS。本文选择的串行EEPROM是93L-C56,因此对应于93LC56的DI、DO、SK、CS这4个管脚。

在计算机加电自检期间,PCI总线的RST#信号复位。PCI9054内部寄存器的默认值作为回应。PCI9054出本地LRESET#信号并检测串行EEP-ROM,若串行EEPROM中的前33个bit不全为1,那么PCI9054确定串行EEPROM非空,用户可通过向9054的寄存器CNTRL的29位写1来加载EEPROM的内容到PCI9054的内部寄存器。配置的信息可在P1xSdk中的PLXMON下对EEPROM进行配置。

EEPROM配置信息主要包括以下两部分:1)PCI配置寄存器,填写生产商ID号、器件ID号、类码子系统ID号和子系统生产商ID号。对于PCI-9054,其生厂商ID号为1OB5,器件ID号为9054,子系统号为9054,子系统ID号为10B5,类码号为0680,表示其为桥设备中的其他桥设备类。 2)本地配置寄存器的配置,即对本地地址空间及其本地总线属性的配置。这些配置要根据实际开发的硬件板卡的硬件资源进行配置。设备人员配置寄存器的任务就是要把某一段本地地址映射为PCI地址,也就是当主机CPU要访问本地地址空间时,要知道其对应的PCI总线地址。

2.2 数据缓存器设计

数据缓存器由两组SRAM组成,在模拟数据时,主机从磁盘阵列上读取要模拟的数据,通过PCI总线的DMA传输给FPGA,首先存到SRAM-A里,SRAM-A存储满时,开始以一定的速率读SRAM-A里的数据,并串转换成串行数据,用LVDS信号形式发送,在读的同时主机启动第二次DMA传输数据给FPGA,再存到SRAM-B,SRAM-A读完、SRAM-B写满就开始以一定的速率读SRAM-B的数据,并串转换成串行数据,用LVDS信号形式发送,这样轮番交替形成“乒乓机制”,有效克服了数据流不连续的现象,解决了形成不间断数据流和两次DMA传输之间的数据间断问题。本文引用地址:http://www.eepw.com.cn/article/191304.htm

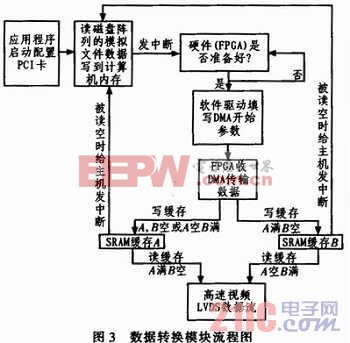

3 工作流程

在设计中,PCI端的数据传输主要是利用PCI9054的BLOCK DMA模式。PCI9054集成了2个相互独立的DMA通道,每个通道都支持Block DMA和Scatter/Gather DMA,通道0还支持Demand DMA传输方式。

Block DMA要求PCI主机或Loeal主机提供PCI和Local的起始地址、传输字节数、传输方向。主机设定DMA开始位启动DMA数据传输,一旦传输完成,PCI9054设定DMA“传输结束位”结束DMA。如果启动中断允许位,在传输结束时PCI9054将向主机(PCI主机或LOCAL主机)产生中断。在DMA传输中,PCI9054既是PCI总线的主控器又是Loeal总线的主控器。

Scatter/Gather DMA要求主机在PCI空间或Local空间设定Descriptor模块,模块包括PCI和Local的起始地址、传输字节数、传输方向和下一个Descriptor模块的地址。PCI9054载人第1个Descriptor模块并发起传输,连续加载下一个模块,直到它侦测到“链结束位”有效,PCI 9054设置“传输结束位”,或者申请PCI或Local中断。这种模式下,PCI9054也可以在每个模块加载时有效中断信号,结束DMA传输。若Desc-riptor模块在本地存储空间,可以编程使DMA控制器在每次DMA传输结束后清除传输字节数。具体工作流程如图3所示。

评论