基于1553B总线协议的解码器设计和FPGA实现

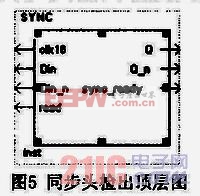

同步头检出模块是检测1553B三种类型字的同步头。如图2所示,命令字和状态字的同步头是先高电平后低电平,数据字的同步头是先低电平后高电平,三种字的同步头的高低电平各占1.5 μs。在用Verilog HDL硬件描述语言设计中,本文通过设置两个计数器,分别在时钟信号上升沿的时候给高低电平计数,理论上说两个计数器都等于24的时候,同步头才算检出。但是要考虑到tco的影响,设计中当两个计数器到等于22的时候,就说同步头检出,这时产生message ready信号,告诉状态机要开启数据处理模块。如图5所示,是同步头检出顶层图。本文引用地址:http://www.eepw.com.cn/article/191237.htm

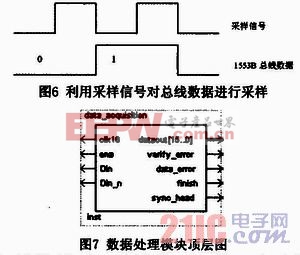

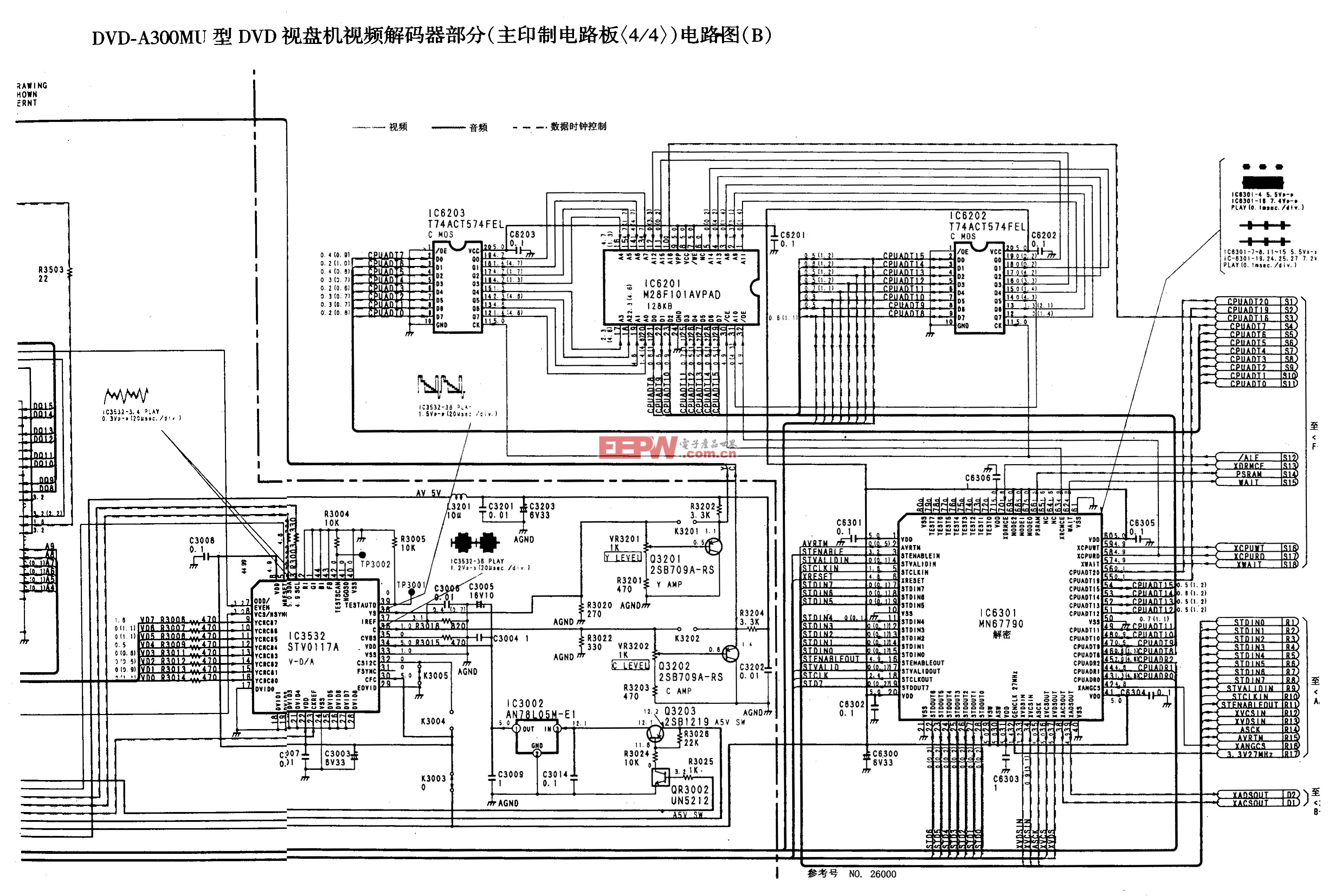

数据处理模块是正确解码后面的有效信息位,包括串并转换、数据错误检测、校验位检测。如图6所示,利用把16MHz时钟8分频产生的2MHz的采样信号对总线数据进行采样,可以在每一码位的1/4周期处和3/4周期处采样,这样采样的信号最可靠。当一码位两次采样的值不一样时,就认为数据正确,并将第一次采样的值发送给数据寄存器。如果一码位两次采样的值相等,就认为数据错误,产生数据错误信号dataerror。当数据寄存器的前十六位的和除以2的余数等于第十七的数据时,就认为奇校验正确。否则就认为错误,并产生奇校验错误信号verify_error信号。图7所示为数据处理顶层图。

评论