CPLD的PLC背板总线协议接口芯片的设计方案

3 基于CPLD 的协议芯片实现

3.1 CPLD 芯片选型。

本设计选用lattice 公司的MachXO 系列芯片,该系列CPLD 集成了部分FPGA 的功能, 除了内置丰富的LUT 资源以外,还有大量分布式的SRAM 位和嵌入式的专用于FIFO 设计的SRAM 块, 并有模拟锁相环(PLL)支持时钟信号的倍频、分频等,I/O引脚可配置成1.2/1.5/1.8/3.3V 电平兼容。

3.2 基于Verilog HDL 语言的硬件程序设计

本设计采用Verilog HDL 语言进行协议芯片的程序设计,Verilog HDL 语言是一种硬件描述语言,设计数字芯片时可以按照层次描述,并可以进行时序建模。本设计采用混合设计模式,主要设计的模块有状态机、协议帧检测、FIFO 控制器设计等。

1)状态机设计。

协议芯片的顶层模块是状态控制器部分,协议芯片共有四个状态, 分别处理基于Verilog HDL 程序语言的状态机描述伪代码如下:

2)协议帧检测。

本协议芯片的帧校验和采用简单的加和形式进行,在接收一方,如果数据帧中有用数据的加和同后续的校验和字节相同,则协议是正确的,否则丢弃该帧。协议帧校验和计算的代码如下:

3)FIFO 设计。

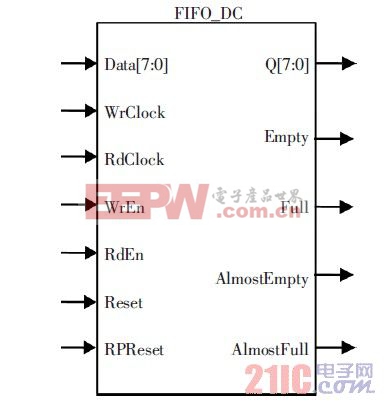

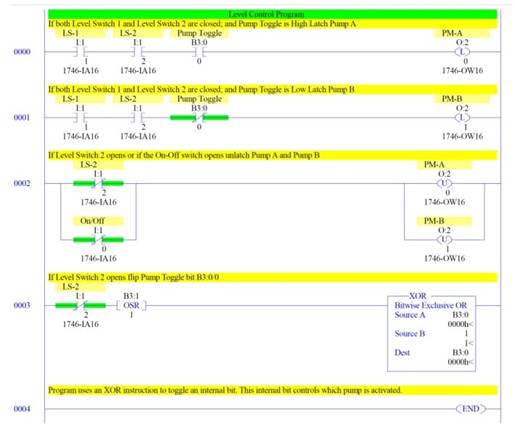

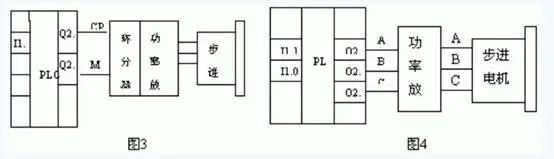

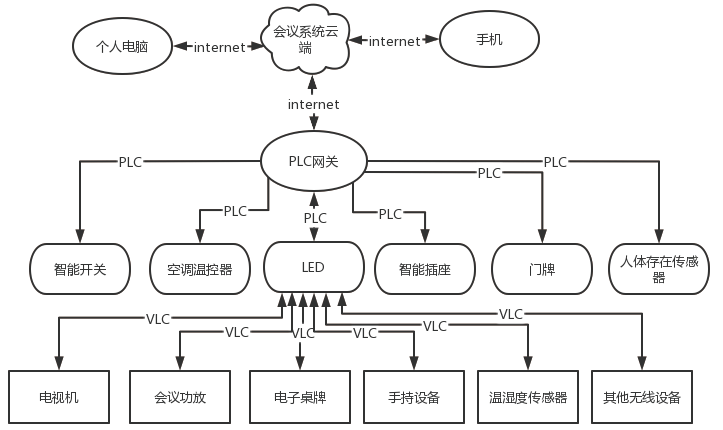

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 块的资源,Lattice 公司的ispLEVER 7.0 软件提供了可配置的IP 软核,该软核可以采用基于嵌入式SRAM 块实现, 也可以使用查找表实现,FIFO 的IP 核框图如图4 所示,FIFO 的可配置参数包括FIFO字节深度、EmptyFull、Almostempty 和AlmostFull触发字节深度、数据宽度、大小端模式等。

图4 可配置FIFO 控制器IP 软核框图

用Verilog HDL 语言实现的发送和接收FIFO控制器的实例代码如下:

3.3 协议芯片综合

Verilog HDL 程序通过Lattice 公司的CPLD 开发软件ispLEVER 7.0 进行编译、综合,多次尝试后最终选择了Lattice 公司MachXO 系列CPLD 中的MachXO2280 芯片, 综合后的主机协议芯片占用CPLD 资源的60%左右, 从机协议芯片占用CPLD资源的45%左右,FIFO 控制器充分利用了MachXO2280芯片内部的嵌入式RAM 块, 同时利用了锁相环实现高频率的时钟工作。最后通过LSC ispVM(R)System 烧写软件经JTAG 口下载到CPLD 芯片中进行协议芯片功能验证测试。

4 结语

本文设计的背板总线协议芯片在背板串行总线时钟频率为25MHz、信号电平为LVTTL,底板引线长度为40cm,1 台主机连接3 台扩展模块的情况下工作稳定并通过了群脉冲试验,验证了这一组协议芯片的设计是成功的。由于该组协议芯片是针对PLC 的周期性和非周期性数据传送专门设计的,硬件实现的协议帧控制器支持高速率通信、支持数据帧检验功能,避免了数据传送的错误,大大降低了外围单片机的软件开销,增强了可靠性,是一组非常适合用于PLC 背板总线或者需要多模块协同工作的背板总线系统协议芯片。

评论