基于FPGA视频图像的Canny算法加速器的设计

4 系统验证和结果分析

为了能清楚直观地验证加速的加速效果,本文在系统平台上对相同的图像分别用加速/未加速的系统做处理,记录相应时间并比较。

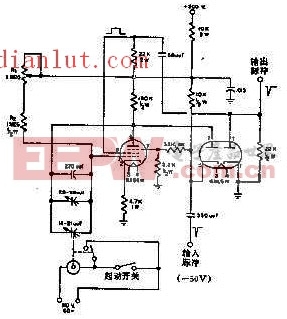

本文采用的验证系统平台以Altera公司CycloneⅡ系列中的EP2C20F484C8芯片为核心搭建而成,如图4所示。在验证系统设计中实现一个串口用来和PC机中的上位机通信,把处理完后的数据经过串口传输给上位机。数据在串口的传输过程中的延迟时间是固定的,故从上位机接收到第一个数据到最后一个数据的时间差即为一帧图像处理所花费的时间。本文引用地址:http://www.eepw.com.cn/article/190119.htm

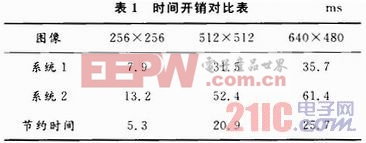

本文选取了不同大小的3幅图片做实验验证,系统时钟频率为100 MHz。其处理时间结果如表1所示,系统1为有加速功能的系统,系统2为未经加速的系统。

由表1可见,经过加速改进后的系统在处理时间上得到了很大的节约,随图像尺寸变大,总的节约时间显然是增加的;且经计算知:当尺寸变4倍(表1第2列256图与第3列512图),节约时间大约增加3.9倍;640×480图比512×512图尺寸大1.17倍,节约时间是1.23倍,实际结果与理论计算相吻合。随着图像尺寸的增加,节约时间亦按比例增加,因此该加速功能在处理大容量高速的图像时具有更大的优势和广阔的应用前景。

图5为一幅在FPGA中经过加速器系统处理后使用Matlab呈现的边缘图像。该算法处理的图像结果基本得到所有的边缘信息,完全能满足应用需求。

5 结论

本文提出并实现了一种基于FPGA的加速Canny算法边缘检测系统。该系统充分发挥和利用FPGA的优良并行处理能力及流水线技术,从而实现功能加速。

在加速过程中通过状态机的控制作用能使模板的运算处理和数据的读/写操作得以同时进行,一定程度上节约了因大量的读/写数据操作而占用的时间。此系统充分利用了FPGA中的硬件资源,大大提高了系统算法的运算效率,且设计结构较为灵活。最终通过边缘检测实验,验证了设计的正确性。

fpga相关文章:fpga是什么

评论