基于双核Nios II系统的数字预失真器设计

3系统功能验证

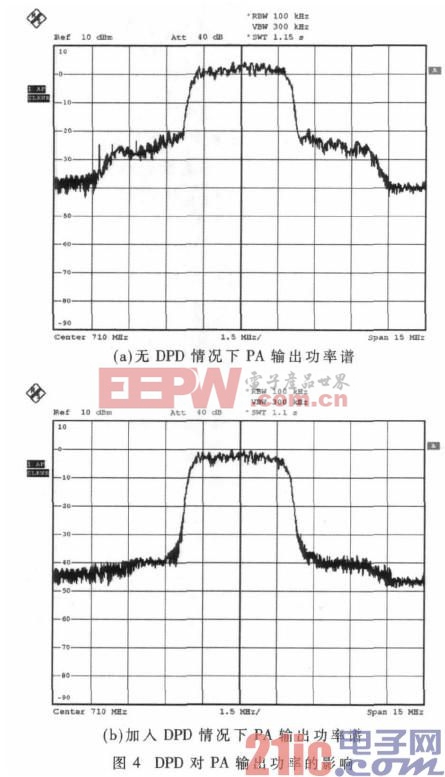

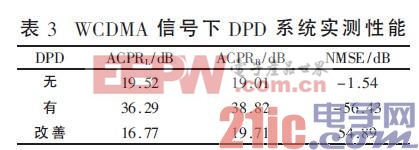

本实验中采用的功放的中心频率为710 MHz,线性增益为43 dB,1 dB压缩点为-8.5 dBm;DPD模型的多项式阶数为3,记忆深度为2,输入到PA的测试信号是具有5 MHz带宽的WCDMA信号。

通过图4和表3可见,WCDMA信号在未加入DPD前,其邻道频谱干扰严重,ACPR只有19 dB.但加入DPD后,信号的带外杂散信号得到抑制,且ACPR改善量在15 dB~20 dB之间。同时,加入DPD后系统的NMSE得到明显改善,WCDMA信号带内失真得到了控制。实验测试表明,DPD的预失真效果理想,达到了预期设计目的。

本设计在FPGA芯片中实现了一个基于双核Nios II的自适应数字预失真器(DPD)。该系统稳定可靠,能够对功放的非线性进行较好的补偿,且能够抑制信号经过功放后的带外频谱滋生,同时提高了信号在带内频谱的平坦度。

评论