基于FPGA的交通路口车流量检测方法研究

2 基于FPGA的硬件仿真

FPGA即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。FPGA在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域得到了广泛的应用。

文中通过使用matlab对上述算法进行仿真,我们可以得到视频图像每一帧的像素信息,并将该信息作为一个数据矩阵储存到后缀名为dat的二进制数据文件中,作为FPGA硬件仿真的输入激励,即像素点检测的输入部分。

基于FPGA平台来完成实时算法的硬件实现,文中根据算法复杂度及资源使用情况,选取Xilinx公司的SpartanIIIXC3S50芯片完成实现。

XC3S50是Xilinx公司推出的SpartanIII系列中资源可用量较少的一款芯片,它包含768个slices、4块18x18乘法器、4块独立RAM(每块RAM容量为18K)。经过综合计算以及筛选,在节约成本的基础上,确定XC3S50为交通信号灯路口的车流量检测算法的硬件实现平台。

电路设计的开发环境采用ise12.4,并使用modelsim6.5se进行硬件电路仿真。本文引用地址:http://www.eepw.com.cn/article/189598.htm

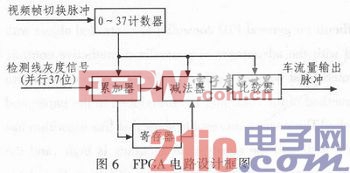

如图6所示,视频帧切换脉冲到来时启动计数器进行时序控制计数,计数到37后保持,等待下一个脉冲的启动,在计数过程中将数值输出至其他电路。累加器接收到计数后,对每一帧更新的并行灰度信号进行逐位累加处理,当37位累加完毕,输出累加结果至减法器。减法器在时序计数控制下将当前帧的累加值与寄存器存放的上一帧灰度累加值做差,将结果输出至比较器。比较器将差值与门限值进行比较,如果超过门限,则输出一个高脉冲,作为有车经过的标志。

仿真采用的系统时钟为65.536 MHz,对应时钟周期约为15.2 ns,如图7所示,每一帧的处理时间仅需38*15.2 ns≈577 ns,可以满足快速处理的需要。图中output_signal为比较器输出的结果,即为监测是否有车辆通过的标志,该结果与matlab算法仿真结果完全一致。该算法实现简单,有很高的实时性和可操作性。

3 结束语

文中的算法是利用Matlab编程实现的,而硬件实现是在isel2.4+modelsim6.5se的环境下编译完成的。通过对一段3分48秒的交通路口视频进行验证,准确率在97%以上。文中与其他实现车流量统计的算法相比较,优点在于完成该算法的硬件实现,且就算法本身而言,实现简单,数据处理量小,处理速度快。但该算法自适应性较弱,容易受到外界干扰影响,需要进一步加强对检测算法的优化和改进研究,以提高检测算法的准确度和自适应性。

评论