基于FPGA的电机测速系统设计

2.3 锁存模块的设计

锁存模块具有存储1 s it数完时,所计数的数据和提供自动复位信号的功能。而且,在按下复位信号时,清除计数数据。当闸门信号en为下降沿时,就将计数模块所得到的数值存入锁存模块。当闸门信号en为‘0’时,程序就输出一个低电平的复位信号,反之则输出高电平的信号。

2.4 动态显示模块的设计

动态显示译码是所有数码管共用数据通道,由位选端选通,每位依次导通。由于人眼具有视觉延迟性,所以观察到的数码管为每一位显示不同的数据,同时显示。

设计利用外部时钟50 MHz分频来实现延迟,延迟系数为62 499。则clock上升沿个数为62 499个时,位选信号加1,下一位导通显示数据。数码管的显示需要将0到9的BCD码转换为七段数码管显示。与分频模块类似,由于时间较长,设计将延迟系数62 499改为8,则clock每8个上升沿则数码管显示下一位。

动态显示模块仿真如图7所示。本文引用地址:http://www.eepw.com.cn/article/189520.htm

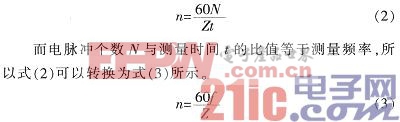

N——电脉冲个数

n——电机转速(单位为:转每分钟)

Z——光电编码器倍增数(此设计中为360)

t——测量时间(单位为:秒)

通过式(1)可以推出电机转速值n的计算公式如式(2)所示。

f——测量频率

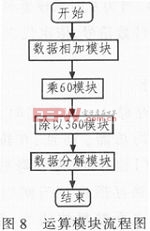

由式(3),程序在运算模块中将会编写的模块有数据相加模块、乘60模块、除360模块和数据分解模块。运算模块流程图如图8所示。

数据相加模块是为了将频率计所得到的四位数值乘以相应的倍数,再将其相加后得到一个整体的二进制数,以便于进行下面的运算。又因为电脉冲的个数单位为个每秒,而电机转速的单位为转每分钟,所以存在60 s的转换值。利用程序将之前得到的数据乘以60。使用的传感器是欧姆龙编码器E6B2-CWZ6C360P/R,所以倍增数是360,所以在运算模块中我们要除去360。在运算得出转速值后,还需要一个将这个二进制数值分解的模块,因为数码管显示模块是将个十百千位单独显示的,所以要先将每一位分解出来,再送入数码管显示。

3 结束语

本次设计是基于FPGA的电机测速系统设计,利用的是Altera公司开发的Quartus II软件作为设计平台,可以在FPGA开发板上实现测量由传感器转换得到的脉冲信号,并且通过计算得到电机转速值。

在本次设计中,还可以进行一些扩展,可以添加报警电路,设定一个报警值,当测量的转速值大于这个报警值时,就可以让蜂鸣器报警或数码管点亮。

评论