基于FPGA的电机测速系统设计

1.3 传感器电路的设计

若要测量转速信号,需要先将其转换为电信号,所以就需要用到光电脉冲传感器。本次设计所选用的光电编码器为欧姆龙编码器E682-CWZ6C360P/R。

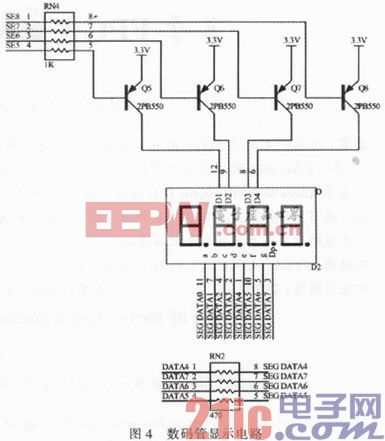

1.4 显示电路的设计

在本次设计中我们用到的显示电路如图4所示。本文引用地址:http://www.eepw.com.cn/article/189520.htm

由数码管显示电路可以知道,这是共阳极数码管。当在位选端SE1~SE4输入低电平时,三极管导通,从而D1~D4接入高电平。由a到DP端输入数码管显示码,就可以得到我们所需要的数字,由位选端让数码管选择导通。

2 FPGA模块设计

FPGA模块的设计主要是实现将由光电编码器转换得到的电信号转换成转速值,通过数码管显示。因此本次设计的模块主要有分频模块、计数模块、锁存模块、数据处理模块和动态显示模块等组成。

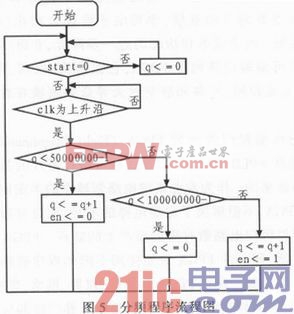

2.1 分频模块的设计

在本次设计中我们需要得到的是转速值,而测量的根本原理就是将转速信号转换为频率信号,同过测量频率信号从而算出转速值。由于外部时钟提供的是50 MHz的时钟信号,此信号送入FPGA模块,通过程序将其进行分频,设计需要的是1 s的闸门脉冲,来统计被测信号的个数,从而计算出被测信号的频率。

分频模块的设计流程图如图5所示。

2.2 四位十进制计数

四位十进制计数模块是通过复位信号和闸门信号来控制模块对外部被测信号的十进制计数。当复位信号为高电平时,b1、b2、b3、b4四位计数信号都为0。当复位信号为低电平,并且闸门信号为高电平时,计数模块开始统计外部信号clk1的个数,b4为最高位,b1为最低位。

评论