一种通用中频数字化接收机的实现

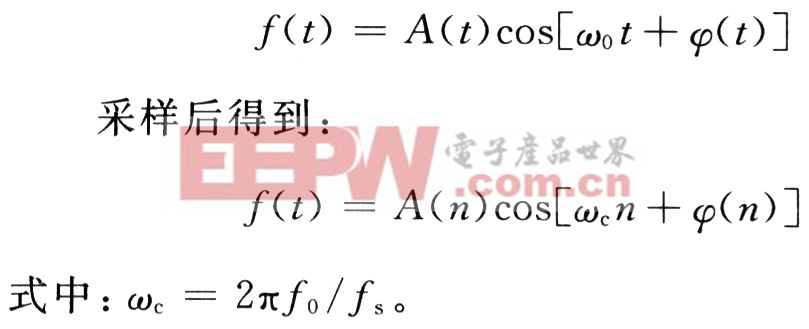

设输入模拟中频信号为:本文引用地址:http://www.eepw.com.cn/article/188825.htm

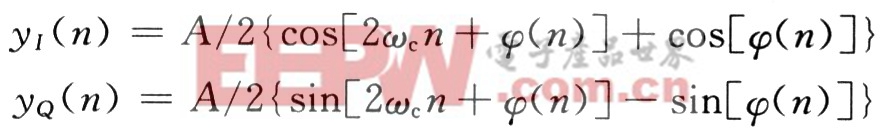

本地数字振荡器(NCO)产生的正交信号为:cos(ωcn)和sin(ωcn),与中频信号在混频器相乘后得:

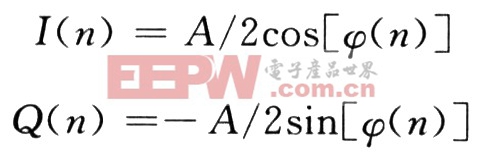

通过低通滤波器滤除倍频分量后,可以得到有用的正交I,Q信号:

由于信号的采样频率较高,也就是上式的I(n),Q(n)速率很高,一般远大于窄带信号的带宽,这时可对其进行速率转换(抽取),以降低此时的输出数据率。不过,抽取后的数据率应不小于信号带宽。在此之前,需经抗混叠滤波器滤波,以保证信号可靠完整地恢复。

图1中的中频信号是中频带限信号,如果此时中频信号的中心频率较低,可取高采样时钟过采样,依Nyquist采样定理,取采样率fs>2fH采样(fH为信号的高端),能够不混叠地恢复原信号。如果此时中频信号的中心频率较高,采样率与信号中心频率的关系不满足Nyquist采样定理条件,这时考虑是否满足带通信号的采样定理。这个定理是中频信号采样的理论依据,而Nyquist采样定理是带通信号采样定理的特例。带通采样定理:如果一个中心频率为fo频率带限信号,其频率限制在(fL,fH)内。

fo=(fL+fH)/2,当采样时钟fs与fo满足关系:

![]()

式中:n取能满足fs≥2B的最大正整数,B=fH-fL,则用fs进行等间隔采样,所得到的信号采样值能准确地确定原信号。

满足式(1)的中心频率为fo的信号经采样时钟fs采样后,f(t) 展开项中 cos(2 πfon/fs) 与sin(2πfon/fs)交替取值为零,当它们不为零时,取±1。可交替得到I,Q样值,不过这时的I,Q值已是经二分之一抽取,时域相差半个采样点,这时的I,Q值要在时间上对齐,符号修正,这样就很方便地实现了下变频。之后,只要将处理后的数据经数字滤波器滤波,按合适的抽取因子抽取就可得到所需的I,Q值。这种方法特别适合用FPGA设计的数字下变频器,不需要NCO,节省了设计数字混频器的逻辑资源,而且早期的商用数字下变频器件也是这种数字混频器,要求fo,fs满足式(1)的关系,如HARIS公司(现为Intersil公司)的HSP43216。

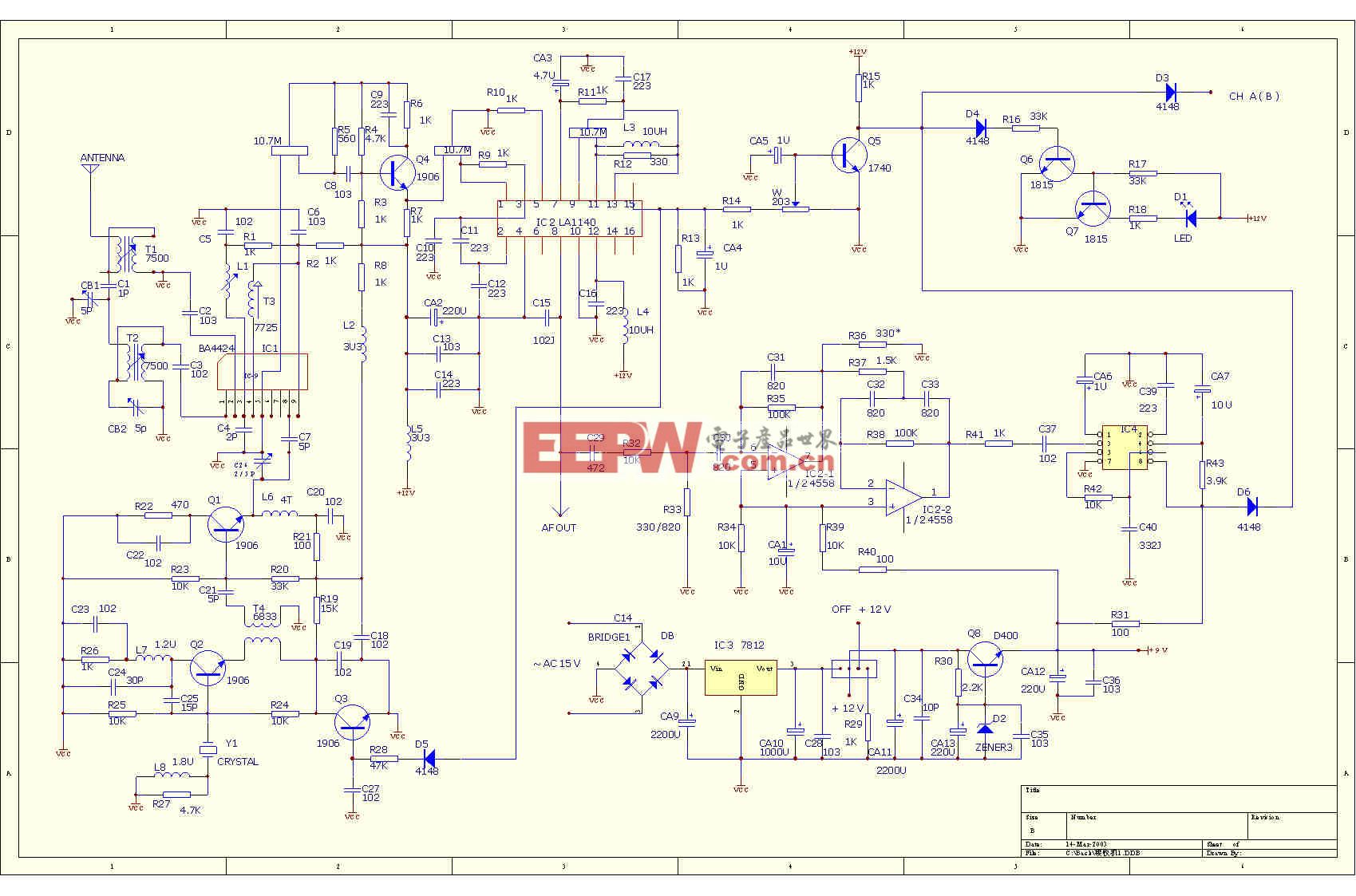

当信号中心频率fo较高,即是高中频信号时,用fs对信号采样属欠采样。当然fo,fs不一定严格满足式(1)的关系。fo,fs选用的总原则是从频谱上分析,采样后的信号经混频、滤波和适当抽取后,基带频谱没有混叠。本设计只是构建一个通用平台,以下的设计用采样率80 MSPS时钟采样,中频信号为中心频率10 MHz,带宽2 MHz,最后输出数据率2.5 MSPS。采样率和信号的最高频率满足过采样关系。

2 器件选用及参数设计

设计中的主要器件:模数转换器和数字下变频器分别选用AD公司的AD6645和Intersil公司的ISL5416,这两款器件都是具有较高性价比的器件。AD6645是高速、高性能的模数转换器,具有14 b,105 MSPS采样率。该芯片是目前用于直接中频采样的性能较好的一款芯片,片内包括采保和参考时钟,提供CMOS兼容的输出,输入信号带宽可到270 MHz。

AD6645的采样时钟要求质量高且相位噪声低,如果时钟信号抖动大,信噪比容易恶化,很难保证精度。为了优化性能,AD6645的采样时钟采用差分形式。时钟信号可通过一个变压器或ECL的差分芯片交流耦合到A/D的时钟输入引脚。

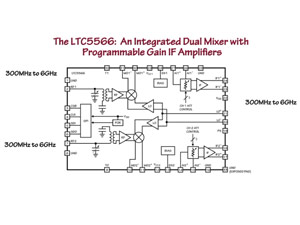

数字下变频器ISL5416是四通道宽带可编程下变频器,专为大动态范围应用而设计,输人数据率最高可达95 MSPS,片内包含数控振荡器(NCO)、数字混频器(Mixer)、数字滤波器(CIC和FIR)、自动增益控制AGC和重采样滤波器等。四个并行16 b定点或17 b浮点输入通道,NCO控制字是32 b可编程的、无杂散动态范围SFDR>110 dB。数字滤波器包括可编程级联的CIC滤波器,两个可编程的FIR滤波器级联,第一个FIR滤波器为32阶,第二个FIR滤波器是64阶,每个数字滤波器后接一个可编程抽取计数器,整个器件的总抽取比可从1~4 096。数字AGC增益范围可达96 dB,,内部数据通道是20 b宽度。

评论