一种通用中频数字化接收机的实现

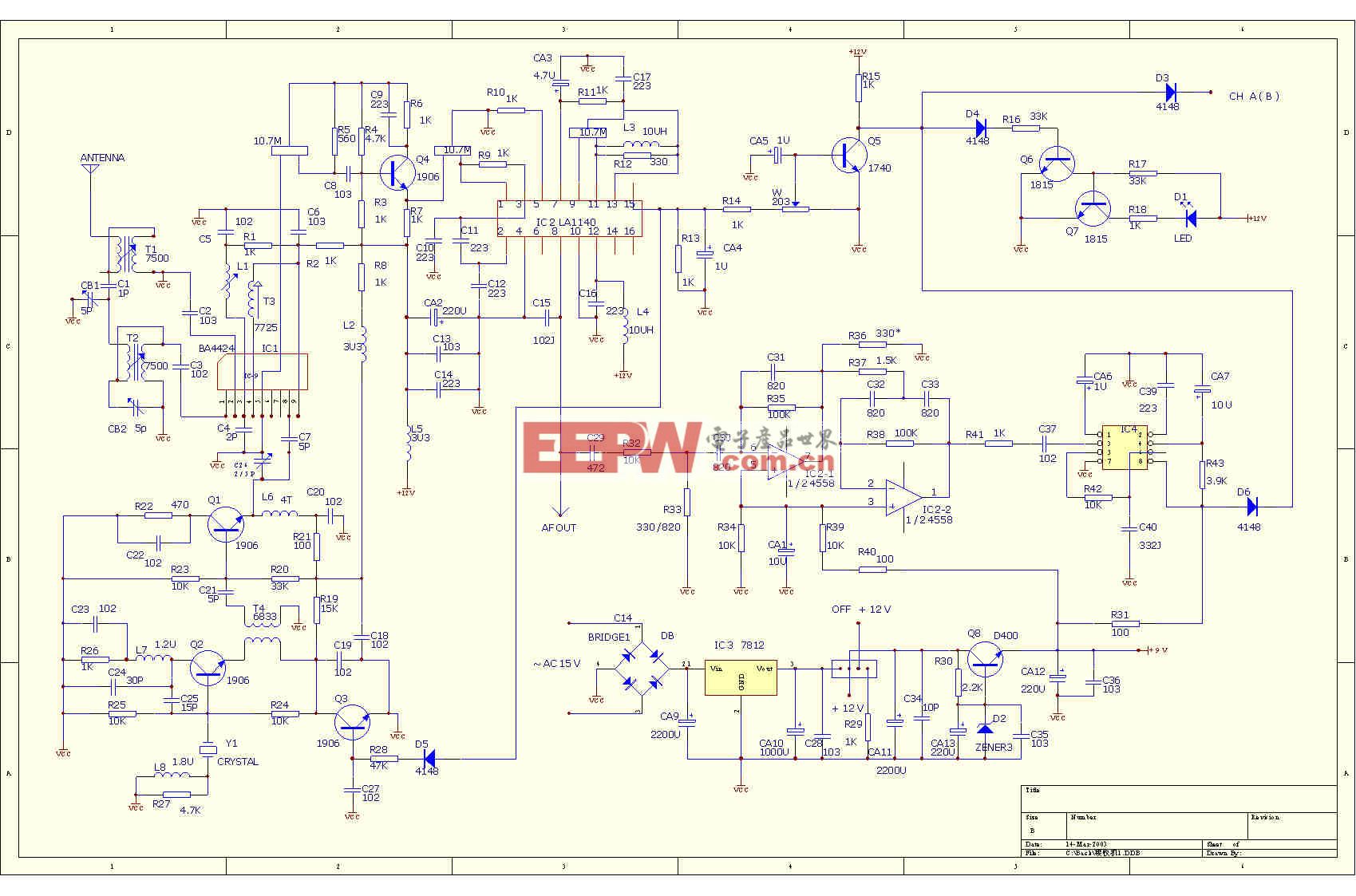

时序控制和信号预处理芯片采用Altera公司的A-PEX系列的一款器件。该芯片包括典型的200 000个逻辑门,片内带有逻辑存储单元,具有106 496 b RAM。运算速度和内部资源能满足时序控制和一般信号处理的要求。这个系统的时序控制电路采用Verilog硬件描述语言编程实现。

本系统采用AD6645实现模数变换,用ISL5416完成数字下变频,用FPGA进行时序控制,再配以外围电路构成中频数字接收机电路。用AD6645结合ISL5416是灵活设计中频数字接收机具有较高性价比的组合。

本设计的主要工作是ISL5416的参数选取,主要是数字下变频器芯片ISL5416的NCO和数字滤波器的参数设计和设置。NCO的频率设置范围为-109~+109Hz,本设计NCO选用10 MHz。中频信号经Mixer混频后,需经抗混叠滤波,首先是CIC滤波器,其后是2级FIR滤波器。CIC一般采取5级级联,5级级联可满足杂波抑制的一般要求。其后第一级FIR滤波器主要是进一步降低CIC后数据率,最大化FIR2的效能,FIR2提供最终的滤波效果。中间包括三次抽取。一般抽取器放在滤波器之后,这样即可滤除高频分量,又可确保输出不混叠。图2是滤波器通道流程图。本文引用地址:http://www.eepw.com.cn/article/188825.htm

FIR滤波器可借用专门的滤波器设计软件或Mat-lab软件设计。抽取因子的选取根据不同采样率或数据率进行选取,总抽取因子为各因子相乘,三个抽取器抽取比的选取,一般考虑将大抽取比放在CIC处,因为CIC只做位和加法运算,不做乘法运算,适合实时处理,灵活方便。经过大抽取后降低了后面FIR滤波器设计的压力。最后经滤波,抽取后总效果应做到心中有数,用Matlab进行仿真,以检验各滤波器设计是否合理。

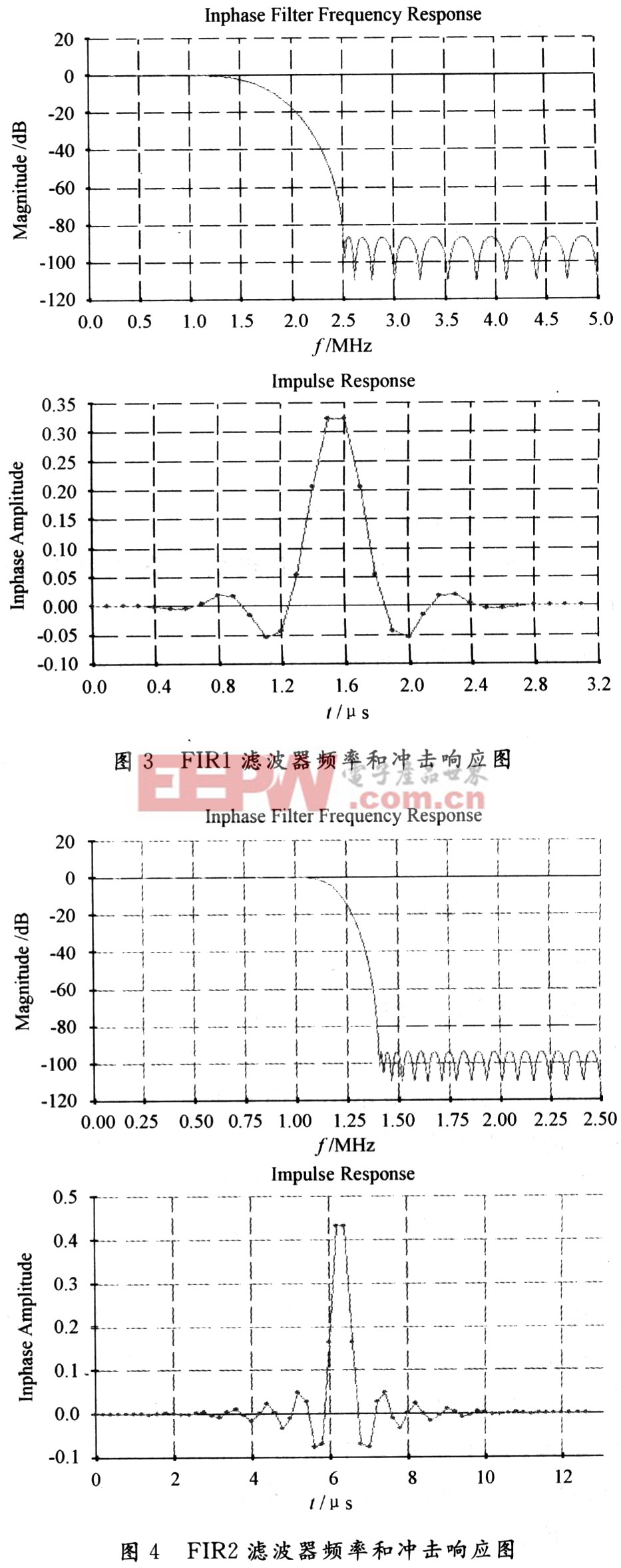

本设计滤波器考虑用5级CIC级联后8级抽取;32阶FIR滤波器后2级抽取;64阶FIR滤波器后2级抽取。这样的总抽取也实现了2.5 MSPS输出数据率。对于FIR1滤波器的设计参数:经8级CIC抽取后,其数据率为10 MHz。选定32阶的FIR滤波器的参数是:采样率10 MHz,通带1 MHz,止带2.5 MHz,通带起伏0.01 dB,阻带衰减80 dB,设计结果如图3所示。

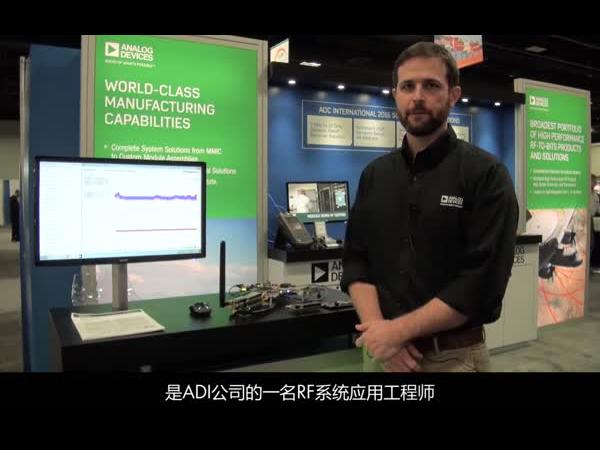

对于FIR2滤波器设计参数:经2级FIR1抽取后,其数据率为5 MHz。选定64阶FIR滤波器的参数是:采样率5 MHz,通带1 MHz,止带1.4 MHz,通带起伏O.01 dB,阻带衰减80 dB,设计结果如图4所示。

ISL5416经8级CIC滤波抽取,2级32阶FIR滤波抽取,2级64阶FIR滤波抽取后总效果用Matlab软件仿真如图5所示。图中显示了3个辛格函数(sinc)的旁瓣。从图5可以看出,带外抑制在90 dBFS以下能够满足实际要求。

评论