天然气体积修正仪数据采集模块设计

天然气在输送、分配和使用过程中,需要对天然气的输送量、分配量和用户用量进行计量。在天然气流量的实用计量中,通常用某一段时间间隔内通过天然气管道输送的天然气总量来表示,即天然气的体积总量。天然气总量的计量对象类型很多,气源售出计量、城市购入计量、区域供气计量和用户用气计量等。目前国内天然气大都使用体积计量的方法,但由于天然气在不同的温度和压力下,气体体积有较为明显的变化,采用简单的体积计量,明显不符合公平交易的原则。如何将工况下的天然气体积通过温度、压力和压缩系数进行修正,从而得到标准状况下的体积,是保证天然气贸易结算公平的关键所在。信息技术的不断发展、计算机技术在计量系统中的广泛应用将会提高天然气的计量精度,加快测量数据的传递速度。

1 仪表总体设计

天然气体积修正仪主要完成天然气流量的自动修正,适于安装在工厂、住宅等环境,实时反映天然气的流量计量情况,并可与上位机进行通信,为上位机管理软件提供数据支持。

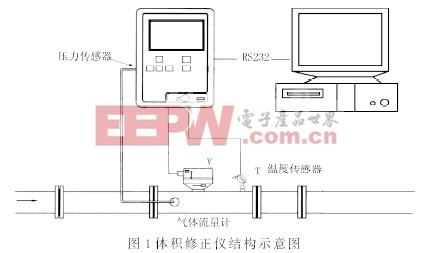

体积修正仪通过压力传感器和温度传感器采集压力和温度信息,结合气体流量计采集的流量脉冲信号进行天然气流量的自动修正,并通过RS232标准进行串口数据传送。图1是体积修正仪的结构示意图。

天然气体积修正仪根据功能设计如下5个模块:数据采集模块、体积修正模块、液晶显示模块、按键模块以及与上位机通信模块。几个功能模块采用低功耗FPGA器件,以Nios Ⅱ嵌入式处理器为核心,利用SoPC技术完成嵌入式开发。

2 数据采集模块设计

在天然气体积修正仪设计中,数据采集模块是保证测量和计算精度的首要模块。分为输入检测和数据处理两部分。

2.1 输入检测

天然气体积修正仪前端测量中涉及2个模拟量:温度和压力信号。根据温度和压力值可计算出天然气的压缩因子,从而校正天然气的体积。

2.1.1 温度检测

照顾到民用和商用的范围,设计采用Pt100陶瓷高性能铂热电阻温度计作为测温元件,铂在氧化性介质中,甚至在高温下的物理、化学性质都很稳定。另外,Pt100温度传感器还具有抗振动、稳定性好、准确度高、耐高压等优点。

本设计气体温度范围为:-30 ℃~70 ℃。经放大电路放大后电压变化范围在0V~4.5 V之间。

2.1.2 压力检测

由于工作压力范围为0~10 MPa,经过选型,采用CGYL-202压力变送器,其三线制输出电压范围为0 V~5 V,配合温度信号,方便后续模数转换。压力变送器采用硅杯压阻传感器为敏感元件,具有体积小、质量轻、结构简单和稳定性好的优点,精度也较高。且具有本安防爆认证,防震性能好。

2.2 A/D转换及数据处理[2]

经采集的温度压力信号在参与压缩因子计算前必须经过模数转换。

本设计采用12位4通道、高速低功耗A/D转换芯片AD7864。AD7864是美国ADI公司生产的逐次逼近式并行输出的A/D转换器,片内由12位ADC、时钟电路、5 V高精度参考电压源和比较器组成,无需任何外部电路即可完成整个A/D转换的过程。该转换器自身带有4路采样/保持电路,可同时进行采样转换,这样就节省了系统的硬件电路空间。该器件最快转换时间可达1.65μs,信号输入范围可为0 V~5 V、±5 V或±10 V。

AD7864的控制状态引脚主要有:

(1)转换启动信号CONVST,下降沿触发一次四通道转换;

(2)工作状态忙信号输出BUSY,高为忙;

(3)读转换结果控制信号RD,低电平有效;

(4)片选信号CS,低电平有效;

(5)转换结束状态输出信号EOC,低电平有效;

(6)通道选择信号线SL1~SL4;

(7)硬件/软件通道选择方式H/S SEL;

(8)第1个数据输出状态信号FRSTDATA,第1通道转换结束数据可读触发为高,第2通道转换结束变为低。

本系统采用EP1C12Q240型FPGA,其足够的引脚资源完全能够满足需求。

2.2.1 数据采集模块总体设计

为了让CPU专注于处理其他任务,专门在FPGA内部设计一个A/D硬件控制器,负责对A/D的采样控制,并将采样数据进行滤波处理。该控制器还可以根据CPU的输出控制字改变采样的频率。

频谱分析的误差很大程度来自采样窗口和实际波形的同步不严格,造成频谱泄漏。为消除频谱泄漏引起的误差,常用的方法有硬件同步和加窗处理。硬件同步的方法比较多,常用的主要有使用PLL电路进行同步。因此,按照GB/T14549-1993要求,用FPGA内部高精度的PLL产生采样时钟来实现严格的同步采样,以保证窗口间无重叠和间隔,并能严格与被测信号频率同步。

在本模块中,所有时序控制均由FPGA完成,采用VHDL语言对FPGA进行配置,配置后的硬件功能包括对A/D转换器的控制、12位并行数据的处理和数据的滤波。

设计2个控制器完成上述功能:A/D控制器和滤波器。A/D控制器用来控制A/D时序,完成A/D转换功能。滤波模块完成数据的后续处理。设计模块图如图2所示。

评论