非陀螺寻北仪信号处理电路的设计与实现

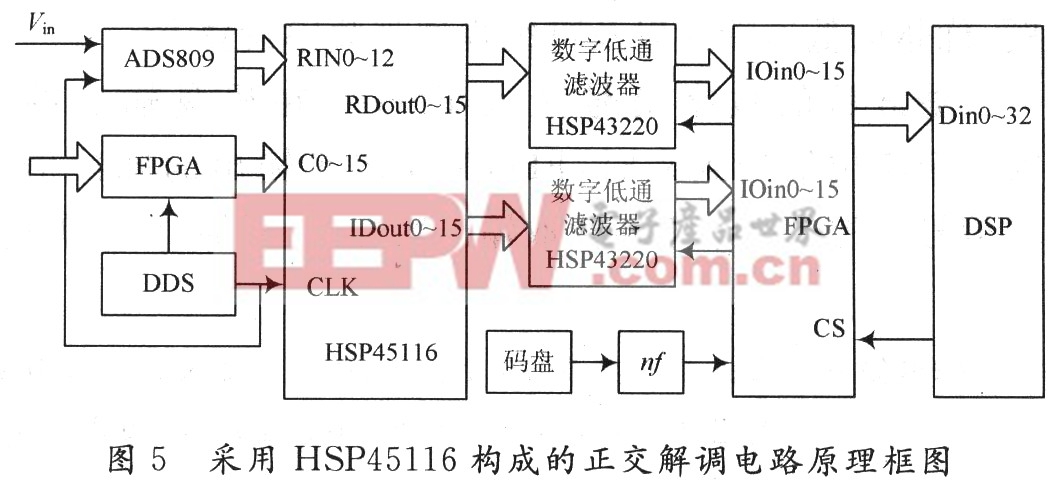

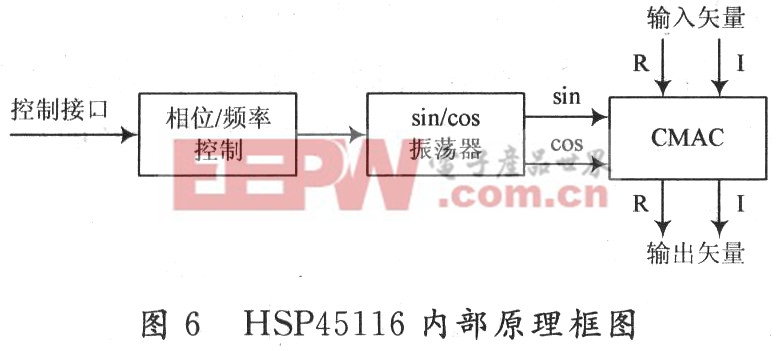

输入信号s(t)首先经过ADS809进行数字化。A/D采样后的数据流进入数字混频器HSP45116,在芯片内数据流分成两路分别与数字振荡器的输出相乘,实现正交变换。HSP45116是一款高性能的数字混频器,最高工作时钟频率为33 MHz,片内包含具有两路正交输出的数字控制振荡器(NCO)和一个16位高速乘法器/累加器。图6是HSP45116内部的简化原理框图。

可以看出,芯片功能分3个主要部分:相位/频率控制、sin/cos振荡器和乘法器/累加器(CMAC)。相位/频率控制由外部控制总线通过FPGA设置相位步进值实现NCO的频率控制,相位累加器为32 b。相位累加器取高20 b输出作为地址查找sin/cos表,于是NCO产生两路正交分量sin和cos。在电路中,为实现中频信号的正交解调,信号从Rin输入,Iin置为0。

系统时钟采用DDS(直接数字合成)形成,可以实现时钟频率、相位以较小分辨率进行改变,因为在系统要求中提到I路和R路输出信号采样率与被测调制信号码元速率成整数倍关系,为了满足这一点,系统时钟同时提供给A/D变换器、HSP45116和HSP43220。另外,系统中还包括FPGA,主要用于对HSP45116和HSP43220的初始化和控制。

经过HSP45116变换后输出的两路数字信号送入集成数字滤波器HSP43220进行数字滤波。HSP43220是一款具有线性相位特性的抽取数字滤波器(DDF),其主要应用特点是高速率数据输入、低速率输出。DDF采用两级串联滤波器结构实现,两级滤波器结合可获得16384的信号抽取能力。信号输出包括24 b信号数据流和DATA RDY信号线。根据系统要求,HSP43220在系统中的主要作用有三个方面:滤除数字正交混频产生的二次谐波分量;灵活和大范围的抽取因子设置解决输出基带信号采样率与码元速率的关联问题;优越的低通特性以及可编程通带频率设置。

滤波后的数字信号送入FPGA,在码盘输出的第一个零位信号到来时,FPGA在码盘输出的脉冲倍频信号的控制线下不断读取输出数据,并累加,在码盘输出的第二个零位信号到来时,停止数据采集和累加运算,并给出数据好信号,从而实现积分运算。DSP通过I/O口读取到FPGA数据好信号后,读出FPGA数据寄存器中的数据,按式(4)计算出寻北仪零位的方位角。

3 结 语

给出了非陀螺寻北仪详细的电路设计思路与具体实现过程。采用高性能的专用数字混频器HSP45116和集成数字滤波器HSP43220来实现非陀螺寻北仪中加速度计输出信号的正交运算和数字滤波,具有良好的信号混频和正交解算性能,既能克服模拟电路固有的误差和系统的不稳定等不足,又减轻DSP的运算负担,满足非陀螺寻北仪所要求的高精度和快速性要求,从而使得非陀螺寻北技术由理论研究转化为实用仪器装备成为了可能。

评论