测控中高精度快速 A/D 采样转换模块设计

随着计算机技术的飞速发展和普及,数据采集系统也迅速地得到应用,在生产过程中, 应用这一系统可对生产现场的工艺参数进行采集、监视和记录,为提高产品质量,降低成 本提供信息和手段。在科学研究中,应用数据采集系统可获得大量的动态信息,是研究瞬 间物理过程的有力工具,也是获取科学奥秘的重要手段之一。尤其是在电路测试与诊断过 程中,为了非常详细、准确地分析电路工作过程中的详细信息,往往需要采集大量的电路 工作过程中电流、电压、功耗等信号变化情况,并将这些采集的信号转换为数字信号以便后台处理。

本文引用地址:https://www.eepw.com.cn/article/188310.htm数据采集的任务,具体地说,就是采集传感器输出的模拟信号并转换成计算机能识别 的数字信号,然后送入计算机或相应的信号处理系统,根据不同需要进行相应的计算和处 理,得出所需的数据;与此同时,将计算机得到的数据进行显示或打印,以便实现对某些 物理量的监视,其中一部分数据还将被控制生产过程中的计算机控制系统用来控制某些物 理量。在电路测试诊断过程中,在故障未被定位之前,需要采集的大量的信号,并快速进 行分析与处理。因此整个信号采集过程中对采集处理芯片、处理算法的选择是非常重要的, 直接关系到测试诊断系统的准确性。

2 A/D 芯片的选取与配置

通过增加ADC 采样位数或提高其采样频率,可以有效降低量化噪声,但由于受工艺等 限制,ADC 的位数限制在一定的范围内,同时兼顾后续处理器实际处理数据能力,保证采 样数据实时处理,ADC 的采样频率不宜太高,否则采集的数据将无法及时处理。对ADC 采 样速率和位数的选择将直接影响着后续微处理器的运算量,因此在本文设计时,必须考虑测 控系统的实时性要求。本系统中微处理器通过中断读取A/D 转换数据,然后进行数字式平 均算法。要在两次中断时间间隔内完成如此多的运算,一方面要求处理器的速度要快;另一 方面要求处理时间间隔尽可能长,此可通过适当增加相邻中断的间隔时间来实现,即降低 ADC 的采样速率实现。从提高信噪比的角度考虑,利用过采样技术,其采样频率越高越好; 但从处理器数据处理的实时性角度出发,采样频率不宜太高。

本文应用的测控系统中,按照测控需求,每个信号周期内通常采样 96 个点,采样值累 加次数为4096 次,若采样频率选择为1 MHZ,则平均每个采样占用时间为0.393216 秒,为 了满足测控实时性的要求。因此本系统设计中,ADC 的采样频率选择为1MHZ。

从存储器存储数据的角度考虑,为了便于传输数据,最后的累加值若利用一个长整形数 据格式(两个字,共32 位)传送,实现传送比较方便,若系统中每点累加次数为4096 次, 则ADC 转换的位数将不超过20 位(212=4096,32-12=20)。根据测控系统实际精度要 求,并借鉴国内外相关电路经验,本文设计采用12 位采样精度即可满足系统实际要求。

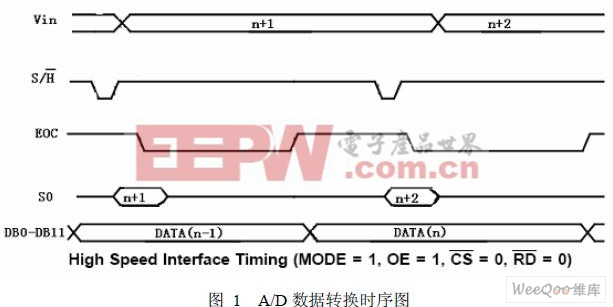

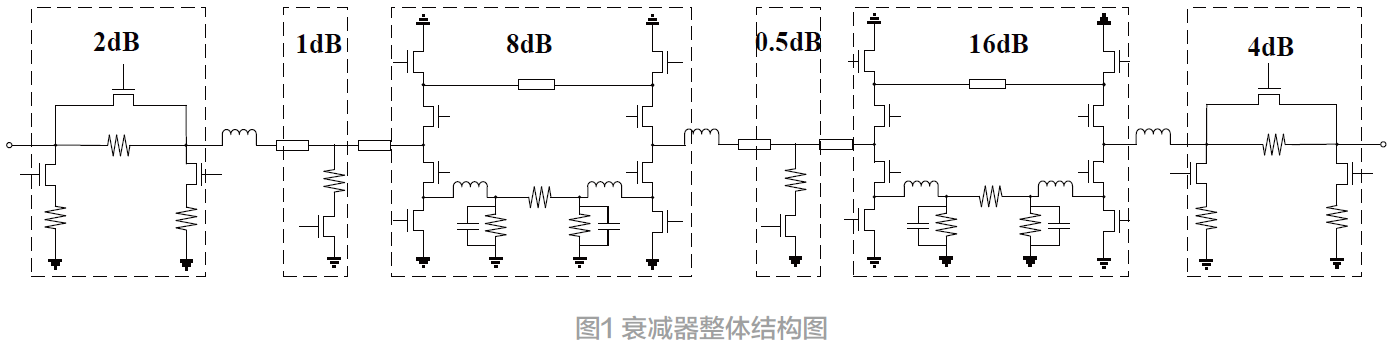

综合以上诸多考虑,本文的ADC 采用NATIONAL semiconductor 公司的ADC12062,内部 自带采样保持电路,12 位采样精度,最高采样频率可达1MHZ,其基准电压为4.096V,则 最小可检测电压为=1mV。ADC12062 采用先进的CMOS 工艺,在高速数据转换时功耗很 低,其功耗仅为75mW,适合于长时间的稳定工作,特别适合于低功耗要求的便携式设备。 芯片的A/D 转换工作时序如图1 所示。

ADC12062 主要引脚的功能介绍:

ADC IN 模拟信号输入引脚,其电压输入范围为-0.005DD4.95V。

/CS 片选信号,低电平有效,ADC 处A/D 转换状态。

/INI 中断输出信号,初始状态为高电平,当AD 转换完成以后,变为低电平时,通知微处理器ADC 转换完成,数据已经在数据线上,可以读取数据。

/RD 读控制信号,低电平有效,和同时为低时,可以读取数据。

S-/H 采样保持信号,下降沿触发。该引脚接入控制采样平台发出的抽样触发脉冲,其下降沿触发信号取样。

/PD 低功耗控制模式,高电平时处于正常工作状态;输入低电平时,进入低功耗模式。

本A/D 转换模块复位以后,ADC 首先处于低功耗状态,直到处理器发送数据采集命令,控制其处于正常的A/D 转换工作状态。

评论