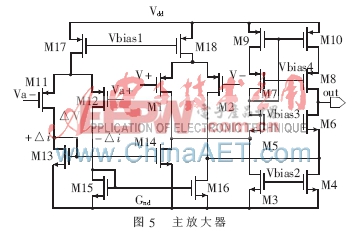

一种斩波失调稳定仪表放大器的研究与设计

本文引用地址:https://www.eepw.com.cn/article/187784.htm

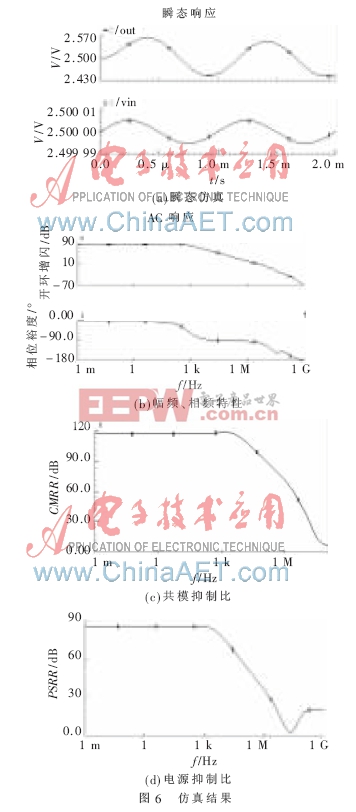

本文引用地址:https://www.eepw.com.cn/article/187784.htm3.3 整体电路的仿真结果

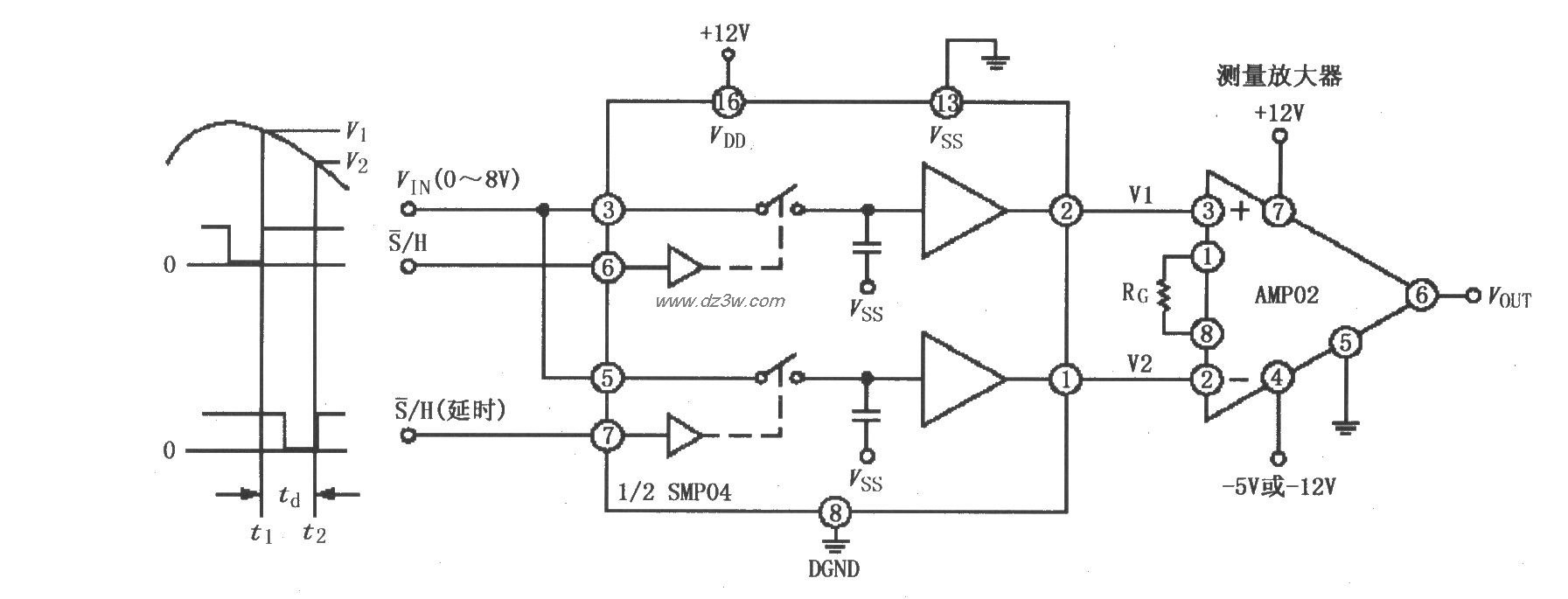

当Vin的瞬态扫描电压幅值为5 μV、频率是1 kHz、AC扫描幅值为1 V、斩波频率为10 kHz,相位补偿电容为0.5 pF时,可以看出开环增益达到87.3 dB,增益带宽积为12.17 MHz,相位裕度在65°以上,CMRR的值为117 dB,PSRR的值大于86 dB。仿真结果如图6所示。

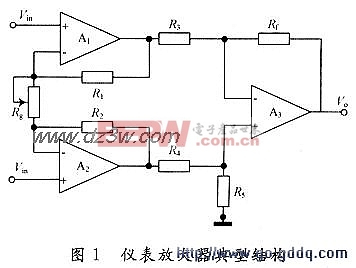

本文应用斩波失调稳定技术设计了一款适用于仪表的放大器,通过对所设计电路进行spectre仿真调整,能够降低1/f噪声和失调电压的影响,电源抑制比、共模抑制比都很高,而且放大器的带宽能比斩波频率高很多,但为了提高系统的驱动能力,还需要在后面接缓冲器。

参考文献

[1] ENZ C C, TEMES G C. Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated doub1e sampling, and chopper stabilization[J]. Proc IEEE, 1996,84:1584-1614.

[2] CHSN P K, NG K A, ZHANG X L . A CMOS chopper-stabilized differential difference amplifier for biomedical integrated circuits[C]. //The 47th IEEE International Midwest Symposium on Circuits and Systems,2004.

[3] DZAHINI D, GHAZLANE H. Auto-zero stabilized CMOS amplifiers for very low voltage or current offset[C]. //IEEE Nuclear Science Symposium, Portland, 2003.

[4] MASUI Y, YSHIDA T, IWATA A. Low power and low voltage chopper amplifier without LPF[J]. IEICE Electronics Express,2008, 22(5):967-972.

[5] SACKINGER E, GUGGENBUHL W. A versatile building block: the cmos differential difference amplifer [J]. IEEE J.Solid State Circuits, 1987,22(2):287-294.

[6] WITTE J F, MAKINWA K A A, HUIJSING J H. A CMOS chopper offset-stabilized opamp[J]. IEEE J. Solid-state Circuits, 2007,42(7):1529-1535.

[7] BABANEZHAD J N, GREGORIAN R. A programmable gain/loss circuit[J]. IEEE J. Solid-State Circuits, 1987,22(6):1082-1089.

评论