采样保持电路中全差分运算放大器的设计与仿真

摘要:本文设计了一种全差分运算放大器,对运算放大器的AC 特性和瞬态特性进行了仿真分析和验证。该运放采用折叠式共源共栅结构、开关电容共模反馈(SC-CMFB)电路以及低压宽摆幅偏置电路,以实现在高稳定下的高增益和大输出摆幅。在Cadence 环境下,基于CSMC 0.6um 工艺模型,进行了仿真分析和验证。结果表明,运算放大器满足设计要求。

本文引用地址:https://www.eepw.com.cn/article/187736.htm1 引 言

运算放大器是许多模拟系统和混合信号系统的一个完整部分,伴随着每一代CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运算放大器的设计不断提出新的挑战。在采样保持电路的设计中,运算放大器是最关键的模块之一,其带宽,摆率,增益,噪声,失调等性能直接决定了采样保持电路模块的速度,精度等性能。

2 折叠共源共栅结构

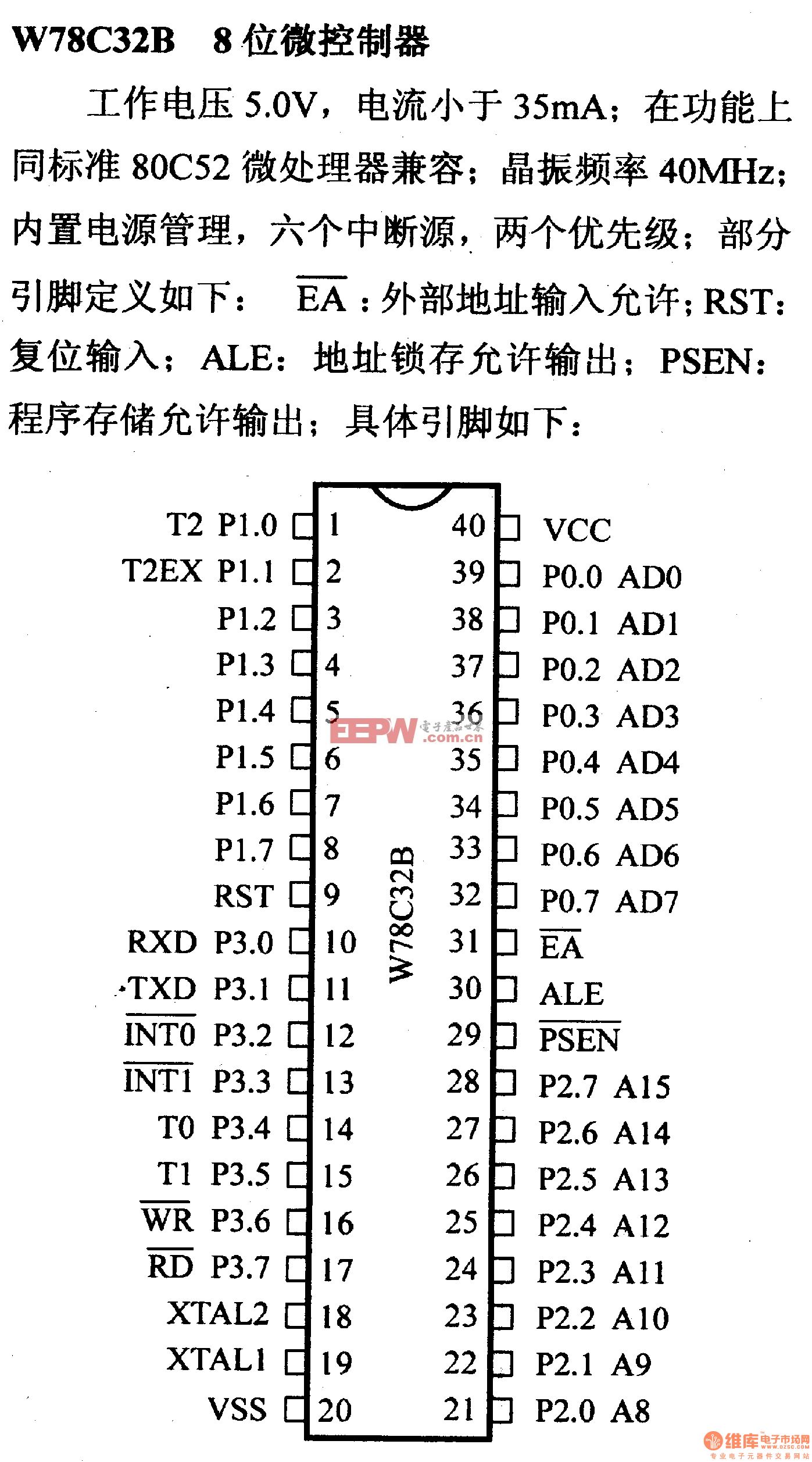

电路结构如图1 所示。

图1 折叠共源共栅运算放大器

运算放大器采用折叠共源共栅结构,采用NMOS 输入差分对MN1 和MN2。MN0 为输入差分对的尾电流源,向MN1 和MN2 提供直流偏置。MP1 和MP2 为电流源,向输入管和共源共栅管提供直流偏置。MP3 和MP4 为共源共栅管,用来提高运算放大器的增益。MN3,MN4,MN5 和MN6 是共源共栅电流镜负载,采用共源共栅结构可以提高输出阻抗。

负离子发生器相关文章:负离子发生器原理

评论