基于DAC5687的高速多通道信号模拟器设计

4 单端高速数据传输线的布线及匹配问题

4. 1 单端高速数据线的阻抗计算模型

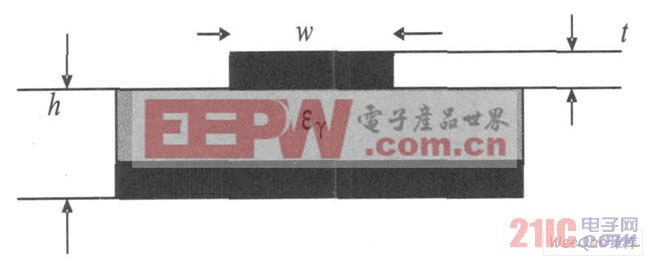

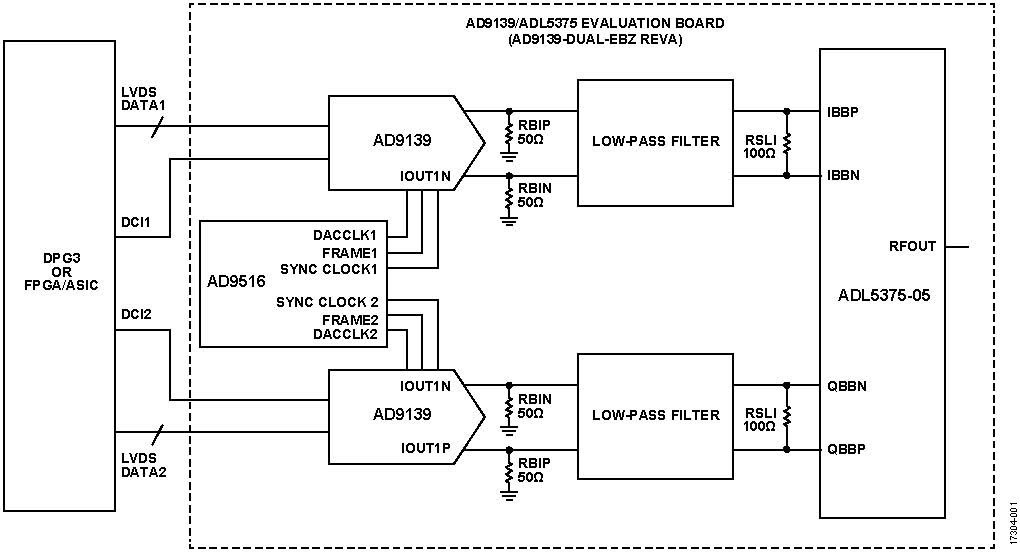

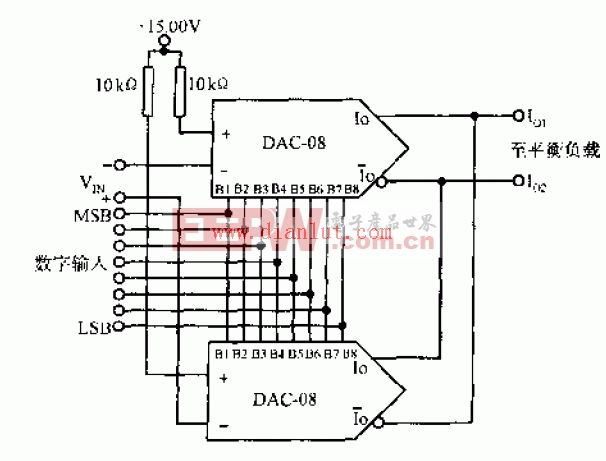

因为DAC5687芯片的两路16bit数据总线接口都是单端的, 即每bit都只对应一根单端传输信号线, 并非是通常高速数据传输所使用的LVDS、LVPECL等差分传输信号线, 所以在印制电路板( PCB )设计时, 就必须考虑高速数据传输情况下的单端数据线布线及终端匹配问题。本设计采用微带线阻抗计算模型和表层走线规则, 以FR4印制板为例进行分析。表层走线应采用微带线模型, 如图2所示。

微带线阻抗计算模型

图2 微带线阻抗计算模型。

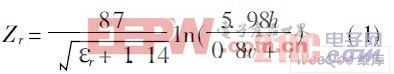

当1. 0 2. 0, 1 εr 15时, 采用如下公式计算: P>

阻抗( Ω) :

传输延时(p s /in ):

其中, h 是对地高度, w 是走线宽度, t是走线厚度, 单位都是in, r 是基板相对介电常数。

例如, 当设计单根传输线阻抗为50Ω, 印制板为FR4, 其介电常数εr = 4. 3, 假设对地高度h =0. 0046in, 走线厚度t= 0. 00137 in (相当于铜层总量1oz )。由( 1)可以计算得到印制电路板走线宽度为0. 008in, 即8m il。

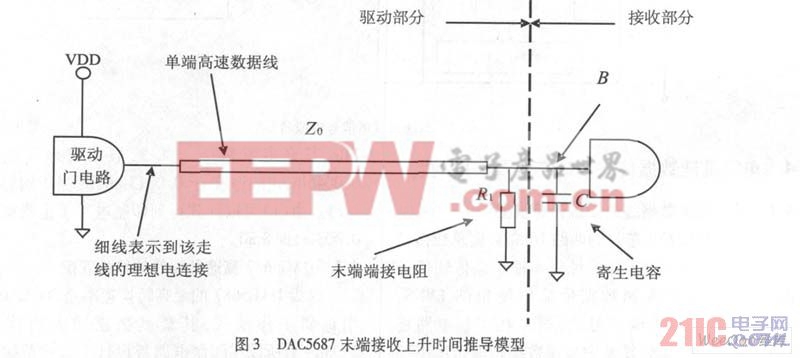

4. 2 DAC5687高速数据线的终端匹配

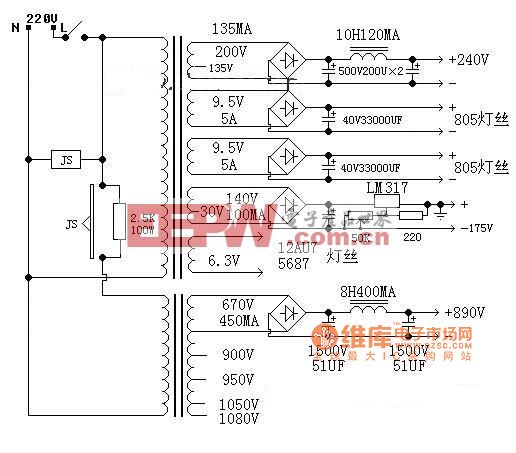

因为DAC5687的最高转换速率是500MSPS, 采用奇偶工作模式, 其最高数据输入的速率为250MSPS, 所以在印制电路板设计上应将单端高速数据线末端上升时间控制在 2ns的范围内。计算模型 如图3所示。

图3

评论