基于DAC5687的高速多通道信号模拟器设计

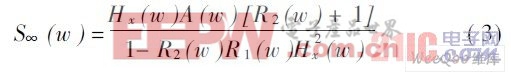

左边部分, 即驱动部分, 由驱动门电路、传输线和端接电阻组成。对于印制板走线, 当连线长度小于上升沿有效长度的1 /6时, 该电路表现为集总系统特征。以FR4板材为例, 由( 2)可计算得到表层走线的上升沿有效长度约为14. 286in。所以, 只要表层走线长度小于2. 38 in 即可采用集总系统模型进行电路布线。但当印制电路板走线的长度大于上升沿的长度的1 /6时, 集总系统模型失效, 应采用分布系统模型讨论。根据传输线理论, 传输线模型的完全响应为:

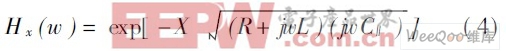

其中,H x (w )是传输线(即单端高速数据线)的传播因数, 当信号频率小于1GH z时, 忽略传输线电导的影响:

其中X 是传输线长度( in), R 是传输线的串连电阻( Ω / in), L 是传输线的串连电感(H / in), C 是传输线的并联电容( F / in)。

A (w )是输入接收函数, 由源端阻抗(即驱动门电路的内阻)Zs (w )和传输线阻抗Z0 (w )共同决定:

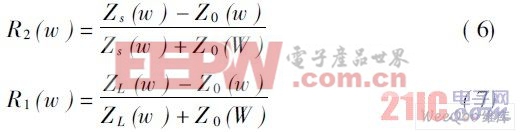

R2 (w )是末端反射函数, R1 (w )是源端反射函数, 分别由( 6) , ( 7)表示:

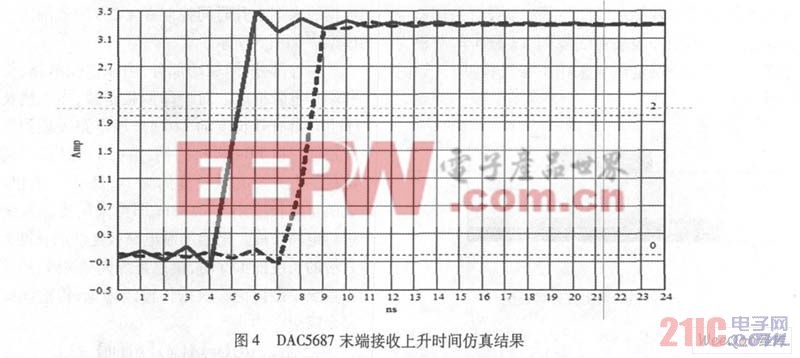

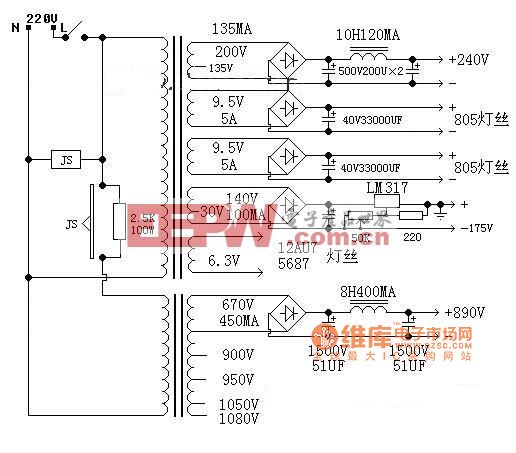

其中ZL (w ) = R1 jwC 根据电路实际参数, 使用Ma thCAD进行脉冲上升时间的仿真, 其中源端阻抗(即驱动门电路的内阻) Zs = 30Ω , Z0 = 50Ω??, C =5pF, 印制板传输线长度X = 4in, 传输线并联电容约为CT = X·C = 12pF, 传输线串联电感约为LT =X·L = 32nH, RT =X·R≈0. 02Ω结果如图4所示。

图4

图4中实线表示驱动门电路的输出脉冲上升沿波形, 虚线表示DAC5687末端接收波形。由于末端电容负载C 的影响, 振铃明显减少, 上升时间增加,末端上升时间仿真结果约为1. 3ns, 实测结果约为1. 5ns, 两者基本相符。

由以上分析可得到结论, 单端高速数据总线的走线应尽可能的短, 并在终端端接匹配负载电阻, 以达到传输线匹配、提高数据传输速率的目的。

5 FPGA 设计

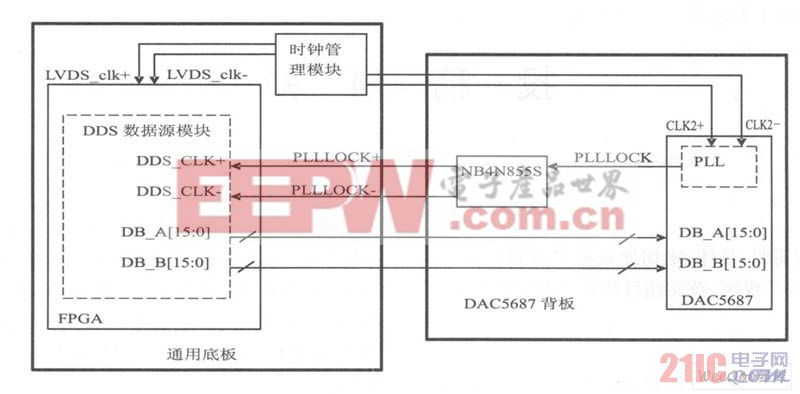

依托通用底板, 针对DAC5687 功能背板进行FPGA 设计。其主要功能一是使FPGA 通过DAC5687 的串行编程接口( SPI) 对DAC5687 的内部寄存器进行设置; 二是实现内部DDS 数据源与DAC5687的严格同步。采用VHDL或V erilog 语言编写程序, 可以简便实现上述功能。DDS 与DAC5687的接口原理如图5所示。

FPGA与DAC5687的数据及时钟接口框图

图5 FPGA与DAC5687的数据及时钟接口框图。

如图所示, 时钟管理模块将分别给FPGA 和DAC5687提供差分工作时钟。DAC5687利用内部锁相环PLL产生数据同步时钟, 经由NB4N855S变换成LVDS差分时钟信号传入FPGA 内部DDS数据源, 作为数据源工作时钟, 以保证信号样点数据和DAC转换工作时钟同步。DDS数据源将产生的A、B两路信号样点数据通过印制板上的单端高速数据总线传输到DAC5687, 最终完成数模转换。

6 结束语

讨论了在CPC I通用底板上设计DAC5687数模转换背板的设计方法, 解决了单端高速数据传输线的布线和终端匹配问题, 为高速多通道信号模拟器提供了一种解决方案。本文引用地址:http://www.eepw.com.cn/article/187651.htm

评论