两类高速ADC之间选择:有缓冲和无缓冲

“有缓冲”或“无缓冲”

本文引用地址:https://www.eepw.com.cn/article/186295.htm考虑输入阻抗的影响时,设计人员一般可以在两类高速ADC之间选择:有缓冲和无缓冲(即采用开关电容)。虽然有许多不同的转换器拓扑结构可供选择,但本文讨论的应用仅涉及流水线架构。

常用的CMOS开关电容ADC无内部输入缓冲器。因此,其功耗远低于缓冲型ADC。外部前端直接连接到ADC的内部开关电容采样保持(SHA)电路,这带来两个问题。

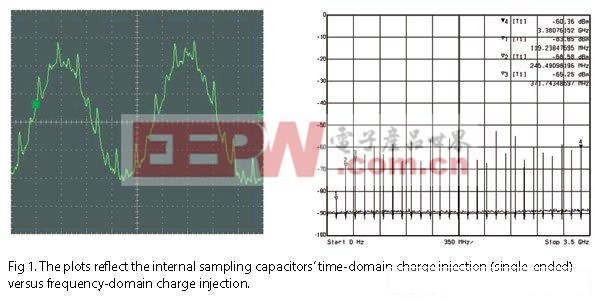

第一,当ADC在采样与保持两种模式之间切换时,其输入阻抗会随频率和模式而变化。第二,来自内部采样电容和网络的电荷注入会将少量信号(与高频成分混合,如图1所示)反射回前端电路和输入信号,这可能导致与转换器模拟输入端相连的元件(有源或无源)发生建立(settling)错误。

图1:此图反映了内部采样电容的时域电荷注入(单端)与频域电荷注入的对比关系。

通常,当频率较低时(《100MHz),这类转换器的输入阻抗非常高(数千Ω左右);当频率高于200MHz时,差分输入阻抗跌落至大约200Ω。输入阻抗的虚部(即容性部分)也是如此,低频时的容抗相当高,高频时逐渐变小到大约1-2pF。“匹配”这种输入结构是个极具挑战性的设计问题,特别是当频率高于100MHz时。

输入端采用差分结构很重要,尤其是对于频域设计。差分前端设计能够更好地对电荷注入进行共模抑制,并且有助于设计。

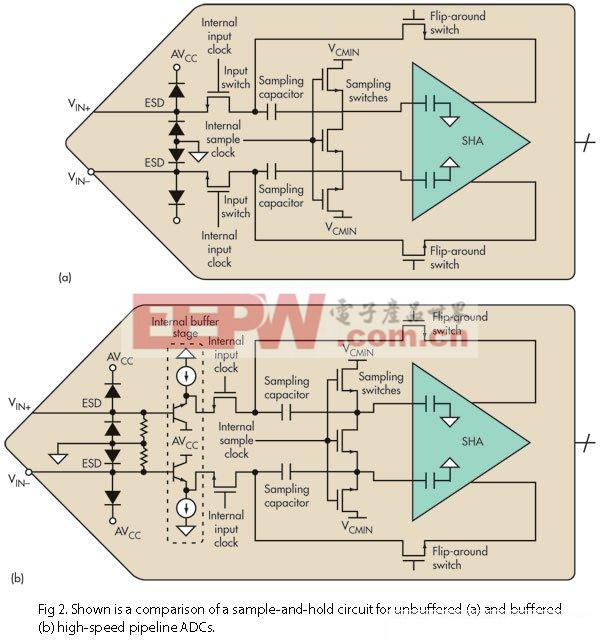

采用带输入缓冲的转换器更便于设计。但不利的一面是这类转换器的功耗更高,因为缓冲器必须设计得具有高线性和低噪声特性。输入阻抗通常规定为固定的差分R||C阻抗。它由一个晶体管级进行缓冲,该级以低阻抗驱动转换过程,因此显著减小了电荷注入尖峰和开关瞬变。

与开关电容型ADC不同,输入终端在转换过程的采样和保持阶段几乎无变化。因此,相比于无缓冲型ADC,其驱动电路的设计容易得多。图2为缓冲型和无缓冲型ADC的内部采样保持电路的结构简图。

图2: 所示是无缓冲(a)和有缓冲(b)高速流水线ADC采样和保持电路的比较。

转换器的选择可能很难,但如今的大部分设计都力求更低功耗,因此设计人员往往采用无缓冲型转换器。如果线性指标比功耗更重要,则通常选用缓冲型转换器。应当注意,无论选择何种转换器,应用的频率越高,则前端设计就越困难。单靠选择缓冲型转换器并不能解决所有问题。不过在某些情况下,它可能会降低设计复杂性。

更多资讯请关注:21ic模拟频道

评论