一种带有增益提高技术的高速CMOS运算放大器设计

摘要:设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14bit精度,100MS/s采样频率的高速流水线(Pipelined)ADC的运放。设计基于SMIC0.25μm CMOS工艺,在Cadence环境下对电路进行Spectre仿真仿真结果表明,在2.5V单电源电压下驱动2 pF负载时,运放的直流增益可达到124 dB,单位增益带宽720 MHz,转换速率高达885 V/μs,达到0.1%的稳定精度的建立时间只需4ns,共模抑制比153dB。

关键词:运算放大器;折叠式共源共栅;高速度;增益提高;三支路电流基准

随着当今集成电路技术遵从摩尔定律的快速发展,在深亚微米级甚至纳米级工艺下电源电压及MOS管特征尺寸不断降低,器件的诸多性能已达到瓶颈。因此,各种高性能模拟或混合集成电路如∑-△调制器、开关电容滤波器和流水线A/D转换器中的高性能运算放大器的研究已成为当今的热点。速度和精度是模拟集成电路中均很重要的性能指标,前者需要器件有大的带宽,短沟道以及单极点系统设计;后者则需要在小偏置电流、长沟道、多级放大器设计的同时实现高增益。因此两者的实现必然会产生设计上的冲突,而这种矛盾也激励着电路设计师去根据应用的需要的同时折中考虑并且创新电路结构来满足系统的要求。

1 电路的选择

1.1 主运放的选择

高速运算放大器作为Pipelined ADC中的一个重要模块,它的特性直接决定了电路系统的整体性能,对于作为ADC前置放大器的设计,运放要有大的单位增益带宽和高的开环增益;同时,要兼顾功耗以及输出摆幅、共模抑制比(CMRR)等参数的考虑。共源共栅结构能够对速度和精度有很好的折中,已广泛应用于运算放大器、基准源和滤波器等模拟器件中,它总的划分有两种结构:套筒式共源共栅结构(telescopic-cascode)和折叠式共源共栅结构(fold-cascode)。

套简式共源共栅运放只有两条支路组成,功耗较小,且由于次主节点附近的寄生电容较小,所以带宽更大,速度更快,但该电路由于是由多级管层叠而成,共模输入范围和输出摆幅过小,如果不接二级电路很难在低压下正常工作;折叠式共源共栅运放的次主极点周围的寄生电容较大,频率特性相对于套简式共源共栅结构较差但差距不大,由于结构呈折叠状而省去了层叠的多层管,其共模输入范围及输出摆幅均远大于套简式共源共栅的对应值,但其结构为4条回路,故其功耗略大。

根据实际需要从应用角度考虑,作为ADC前置放大器,所设计的运放要求要在能保证精度基础上有尽可能快的速度。上述分析表明,两种基本的共源共栅结构所构成的运放均有较高的速度,但是相对而言折叠式共源共栅比套筒式共源共栅有更大的共模输入范围和输出摆幅,且其输入输出可以短接而且输入共模电平更容易选取,因此折叠是共源共栅运放更符合要求。

1.2 增益提高(gain boosting)技术

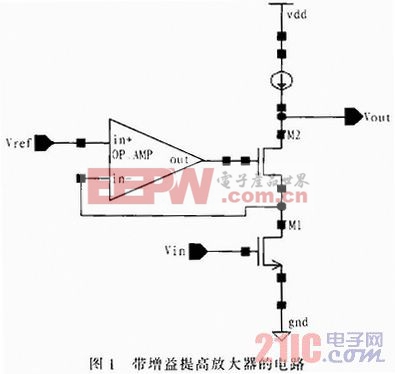

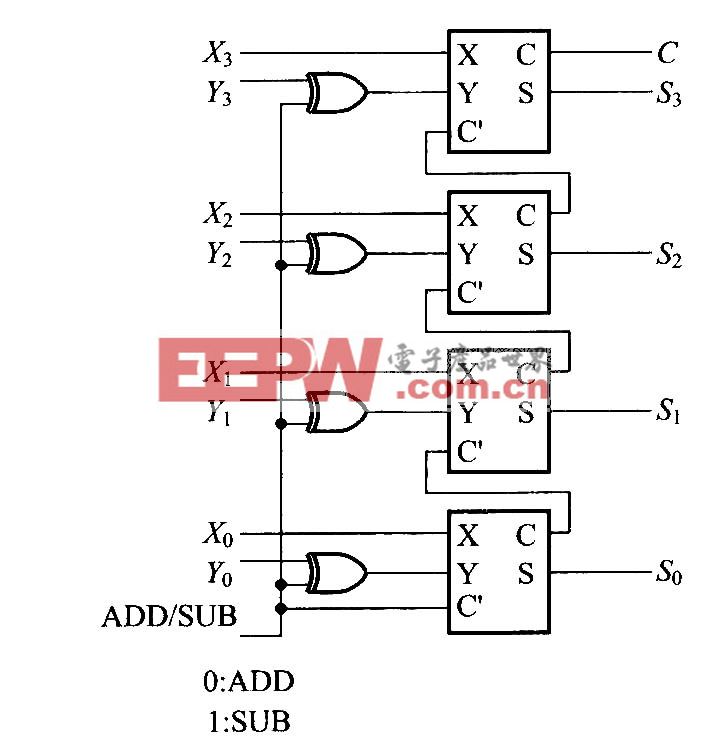

在深亚微米及纳米级工艺水平下MOS管最小沟道长度越来越小,器件的带宽越来越大从而速度越来越快,但增益却越来越低,单级共源共栅运放的增益也降至约40dB左右,这样的结构很难满足对精度的基本要求,故本设计增加了增益提高级。其基本原理如图1所示;将M1看成一个反馈电阻,与M2构成一个从电流到电压的负反馈环路,通过减小由输出到输入管漏极的反馈,使得M1的漏电压随输出电压的变化很小,流过M1的电流更加稳定,因而产生了更高的输出阻抗。设辅助运放Aadd放大倍数为A,则输出阻抗为:

Rout=(gm2ro2(A+1)+1)ro1+ro2 (1)

其中,ro1、ro2分别是M1、M2管得小信号等效电阻,gm2是M2的跨导。可见利用增益增强技术可以是输出电阻提高A倍,从而也使得电路的直流增益增大了A倍:

Alot=gmiro1(gm2ro2(A+1)+1) (2)

但增益增强技术在提高增益的同时也带来一个明显的缺点:在图1电路中得输出端和M1的漏端分别形成运放的主极点和次主极点。因此经常会在辅助运放的单位增益带宽附近产生零极点对,尽管不会影响运放的频率响应,但它却使运放的建立特性变差。通常的处理方法是提高零极点对的发生频率,即提高辅助运放的单位增益带宽,但若将辅助运放的单位增益带宽频率提高到主运放的第二极点附近时,整个运放将不稳定。因此,通过分析得出使辅助运放Aackl的单位增益带宽要介于运放闭环-3 dB带宽和主运放的非主极点值之间,并在辅助运放输出端和地之间增加补偿电容C0和C1进行微调即可,其大小约为负载电容的1/2~1/3。

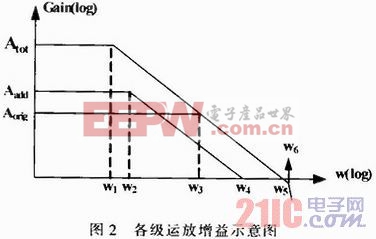

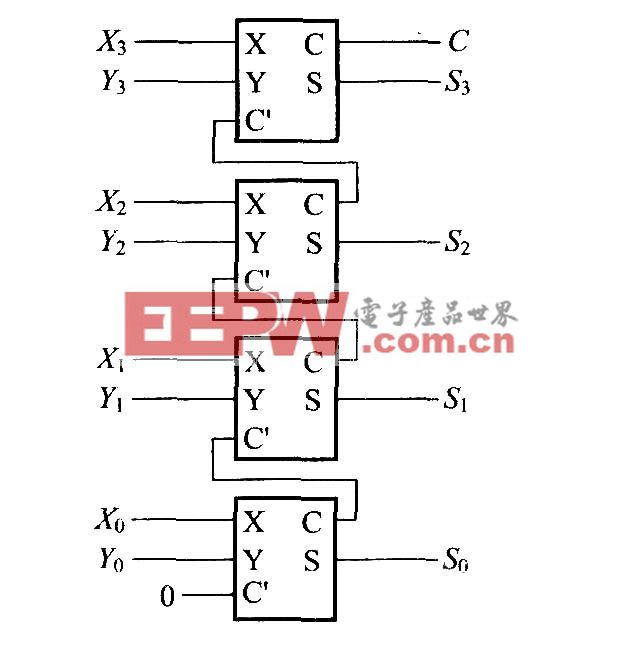

图2是各级运放的增益带宽关系示意图。Aorig为未加增益辅助运放的增益曲线,Aackl为辅助运放增益曲线,Alot为添加辅助运放后主运放的增益曲线。若要使系统稳定,则需:

w3w4w6 (3)

评论