同步整流技术及其在DC/DC变换器中的应用

摘要:同步整流技术是采用通态电阻极低的功率MOSFET来取代整流二极管,因此能大大降低整流器的损耗,提高DC/DC变换器的效率,满足低压、大电流整流的需要。首先介绍了同步整流的基本原理,然后重点阐述同步整流式DC/DC电源变换器的设计。

关键词:同步整流;磁复位;箝位电路;DC/DC变换器

1 同步整流技术概述

近年来随着电源技术的发展,同步整流技术正在向低电压、大电流输出的DC/DC变换器中迅速推广应用。DC/DC变换器的损耗主要由3部分组成:功率开关管的损耗,高频变压器的损耗,输出端整流管的损耗。在低电压、大电流输出的情况下,整流二极管的导通压降较高,输出端整流管的损耗尤为突出。快恢复二极管(FRD)或超快恢复二极管(SRD)可达1.0~1.2V,即使采用低压降的肖特基二极管(SBD),也会产生大约0.6V的压降,这就导致整流损耗增大,电源效率降低。举例说明,目前笔记本电脑普遍采用3.3V甚至1.8V或1.5V的供电电压,所消耗的电流可达20A。此时超快恢复二极管的整流损耗已接近甚至超过电源输出功率的50%。即使采用肖特基二极管,整流管上的损耗也会达到(18%~40%)PO,占电源总损耗的60%以上。因此,传统的二极管整流电路已无法满足实现低电压、大电流开关电源高效率及小体积的需要,成为制约DC/DC变换器提高效率的瓶颈。

同步整流是采用通态电阻极低的专用功率MOSFET,来取代整流二极管以降低整流损耗的一项新技术。它能大大提高DC/DC变换器的效率并且不存在由肖特基势垒电压而造成的死区电压。功率MOSFET属于电压控制型器件,它在导通时的伏安特性呈线性关系。用功率MOSFET做整流器时,要求栅极电压必须与被整流电压的相位保持同步才能完成整流功能,故称之为同步整流。

为满足高频、大容量同步整流电路的需要,近1同步整流技术概述近年来随着电源技术的发展,同步整流技术正在向低电压、大电流输出的DC/DC变换器中迅速推广应用。DC/DC变换器的损耗主要由3部分组成:功率开关管的损耗,高频变压器的损耗,输出端整流管的损耗。在低电压、大电流输出的情况下,整流二极管的导通压降较高,输出端整流管的损耗尤为突出。快恢复二极管(FRD)或超快恢复二极管(SRD)可达1.0~1.2V,即使采用低压降的肖特基二极管(SBD),也会产生大约0.6V的压降,这就导致整流损耗增大,电源效率降低。举例说明,目前笔记本电脑普遍采用3.3V甚至1.8V或1.5V的供电电压,所消耗的电流可达20A。此时超快恢复二极管的整流损耗已接近甚至超过电源输出功率的50%。即使采用肖特基二极管,整流管上的损耗也会达到(18%~40%)PO,占电源总损耗的60%以上。因此,传统的二极管整流电路已无法满足实现低电压、大电流开关电源高效率及小体积的需要,成为制约DC/DC变换器提高效率的瓶颈。

同步整流是采用通态电阻极低的专用功率MOSFET,来取代整流二极管以降低整流损耗的一项新技术。它能大大提高DC/DC变换器的效率并且不存在由肖特基势垒电压而造成的死区电压。功率MOSFET属于电压控制型器件,它在导通时的伏安特性呈线性关系。用功率MOSFET做整流器时,要求栅极电压必须与被整流电压的相位保持同步才能完成整流功能,故称之为同步整流。

为满足高频、大容量同步整流电路的需要,近年来一些专用功率MOSFET不断问世,典型产品有FAIRCHILD公司生产的NDS8410型N沟道功率MOSFET,其通态电阻为0.015Ω。Philips公司生产的SI4800型功率MOSFET是采用TrenchMOSTM技术制成的,其通、断状态可用逻辑电平来控制,漏-源极通态电阻仅为0.0155Ω。IR公司生产的IRL3102(20V/61A)、IRL2203S(30V/116A)、IRL3803S(30V/100A)型功率MOSFET,它们的通态电阻分别为0.013Ω、0.007Ω和0.006Ω,在通过20A电流时的导通压降还不到0.3V。这些专用功率MOSFET的输入阻抗高,开关时间短,现已成为设计低电压、大电流功率变换器的首选整流器件。

2 同步整流的基本原理

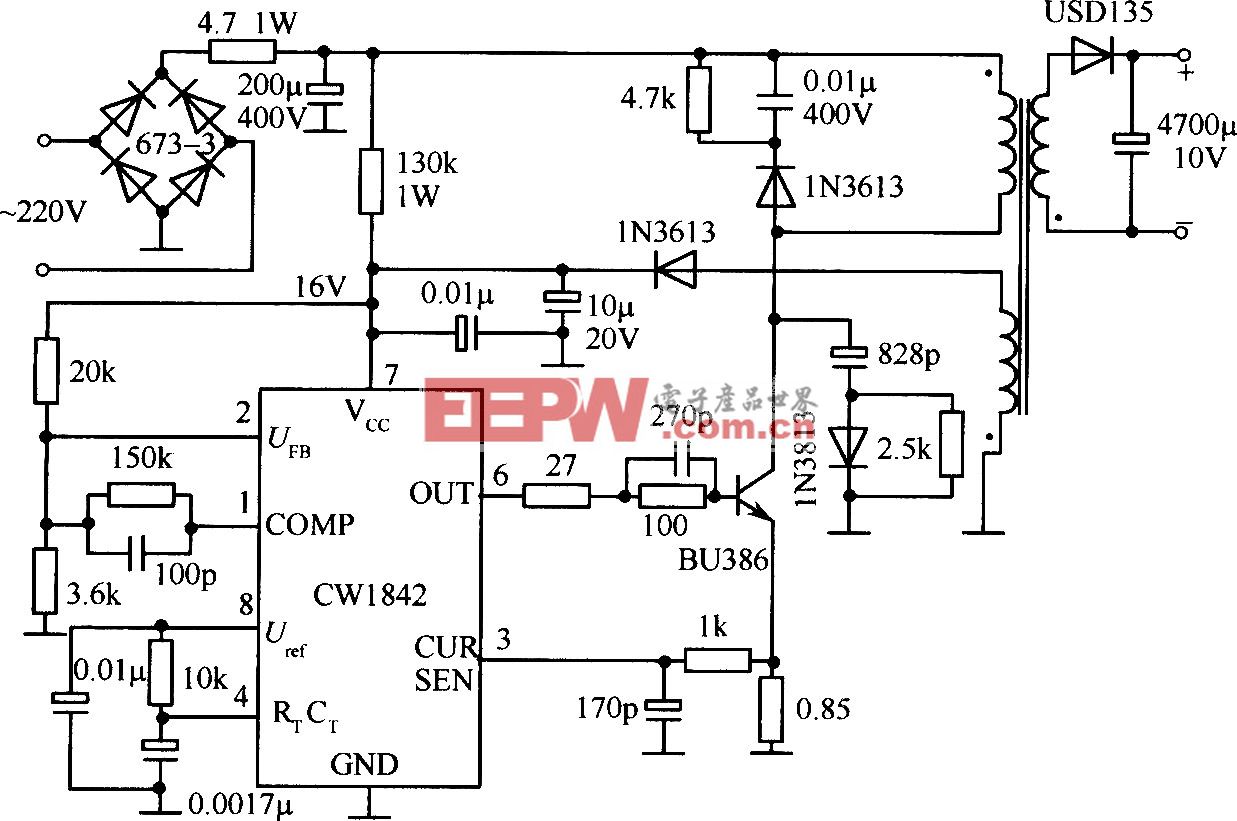

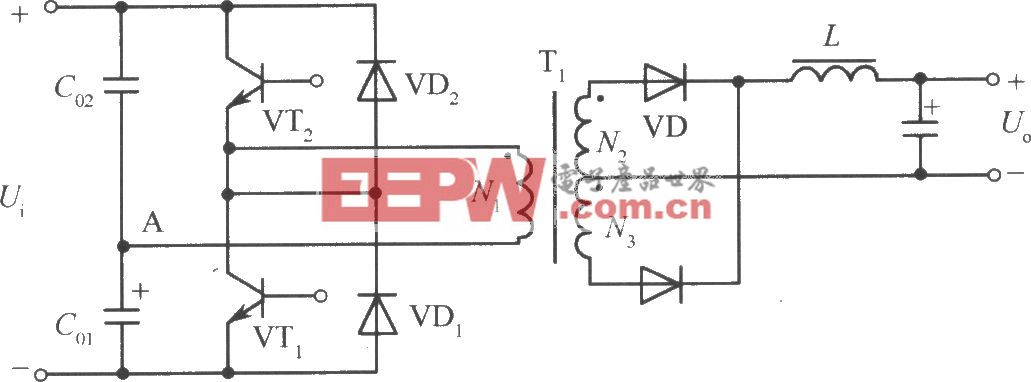

单端正激、隔离式降压同步整流器的基本原理如图1所示,V1及V2为功率MOSFET,在次级电压的正半周,V1导通,V2关断,V1起整流作用;在次级电压的负半周,V1关断,V2导通,V2起到续流作用。同步整流电路的功率损耗主要包括V1及V2的导通损耗及栅极驱动损耗。当开关频率低于1MHz时,导通损耗占主导地位;开关频率高于1MHz时,以栅极驱动损耗为主。

正激式DC/DC变换器的缺点是在功率管截止期间必须将高频变压器复位,以防止变压器磁芯饱和,因此,一般需要增加磁复位电路(亦称变压器复位电路)。图2示出单端降压式同步整流器常用的3种磁复位电路:辅助绕组复位电路,R,C,VDZ箝位电路,有源箝位电路。3种磁复位的方法各有优缺点:辅助绕组复位法会使变压器结构复杂化;R,C,VDZ箝位法属于无源箝位,其优点是磁复位电路简单,能吸收由高频变压器漏感而产生的尖峰电压,但箝位电路本身也要消耗磁场能量;有源箝位法在上述3种方法中的效率最高,但提高了电路的成本。

磁复位要求漏极电压要高于输入电压,但要避免在磁复位过程中使DPA-Switch的漏极电压超过规定值,为此,可在次级整流管两端并联一个RS、CS网络,电路如图3所示。该电路可使高频变压器在每个开关周期后的能量迅速恢复到一个安全值,保证UD>UI。当DPA-Switch关断时,磁感应电流就通过变压器的次级绕组流出,利用电容CS使磁感应电流减至零。CS的电容量必须足够小,才能在最短的关断时间内将磁感应电流衰减到零;但CS的电容量也不能太小,以免漏极电压超过稳压管的箝位电压。电阻RS的电阻值应在1~5Ω之间,电阻值过小会与内部寄生电感形成自激振荡。上述磁复位电路适用于40W以下的开关电源。

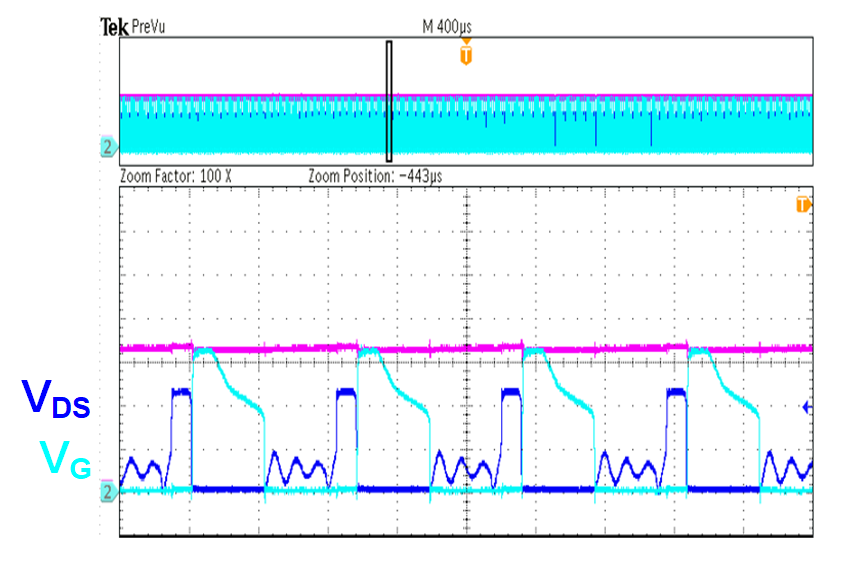

当输入电压为最小值或最大值时,要求磁复位电路都能按可控制的范围将高频变压器准确地复位。检查磁复位情况的最好办法是观察DPA-Switch的漏极电压波形。以图3所示的磁复位电路为例,当输入电压依次为72V、48V和36V时,用示波器观察到3种磁复位波形分别如图4所示。

图4(a)给出了当输入电压为72V时的漏极电压波形。在输出整流管上并联2.2nF的复位电容,可满足满载情况下的需要。初级绕组上的箝位电容取47pF。图中的T表示开关周期,D为占空比,tON=DT为DPA-Switch的导通时间。在tON时间段,高频变压器的正向磁通量增大,漏极电压达到最小值。在tRZ时间段高频变压器被复位,储存在高频变压器中的全部能量接近于零,漏极电压达到最大值。在tRN时间段,高频变压器的负向磁通量增大,此时复位电容和箝位电容向变压器电感放电。在tVO时间段内磁通量保持为负值,此时高频变压器初级绕组的电压为零,这是因为漏极电压与输入电压大小相等(都是72V)而极性相反,互相抵消了。在tVO时间段,负向磁感应电流通过次级绕组。

图4(b)给出了当直流输入电压为48V时的漏极电压波形。随着输入电压的降低,占空比开始增大。在tRZ及tRN时间段内的情况与输入电压为72V时的情况相同,但在tVO时间段高频变压器中的能量接近于零。

图5

2.3 箝位电路

当功率MOSFET由导通变成截止时,在开关电源的一次绕组上就会产生尖峰电压和感应电压。其中的尖峰电压是由高频变压器漏感(即漏磁产生的自感)而形成的,它与直流高压UI和感应电压UOR叠加后很容易损坏MOSFET。为此,必须增加箝位保护电路,对尖峰电压进行箝位或吸收。箝位电路分无源箝位、有源箝位两种。无源箝位电路主要有以下4种设计方案:

1)利用瞬态电压抑制器(TVS)和超快恢复二极管(SRD)组成的箝位电路;

2)利用阻容元件和超快恢复二极管组成的R、C、SRD箝位电路;

3)由阻容元件构成RC吸收电路;

4)由几只高压稳压管串联而成的箝位电路,专门对漏-源电压uDS进行箝位。

上述方案中以1)的保护效果最佳,能充分发挥TVS响应速度极快、可承受瞬态高能量脉冲之优点,方案2)次之。鉴于压敏电阻器(VSR)的标称击穿电压值(U1mA)离散性较大,响应速度也比TVS慢很多,在开关电源中一般不用它构成漏极箝位保护电路。

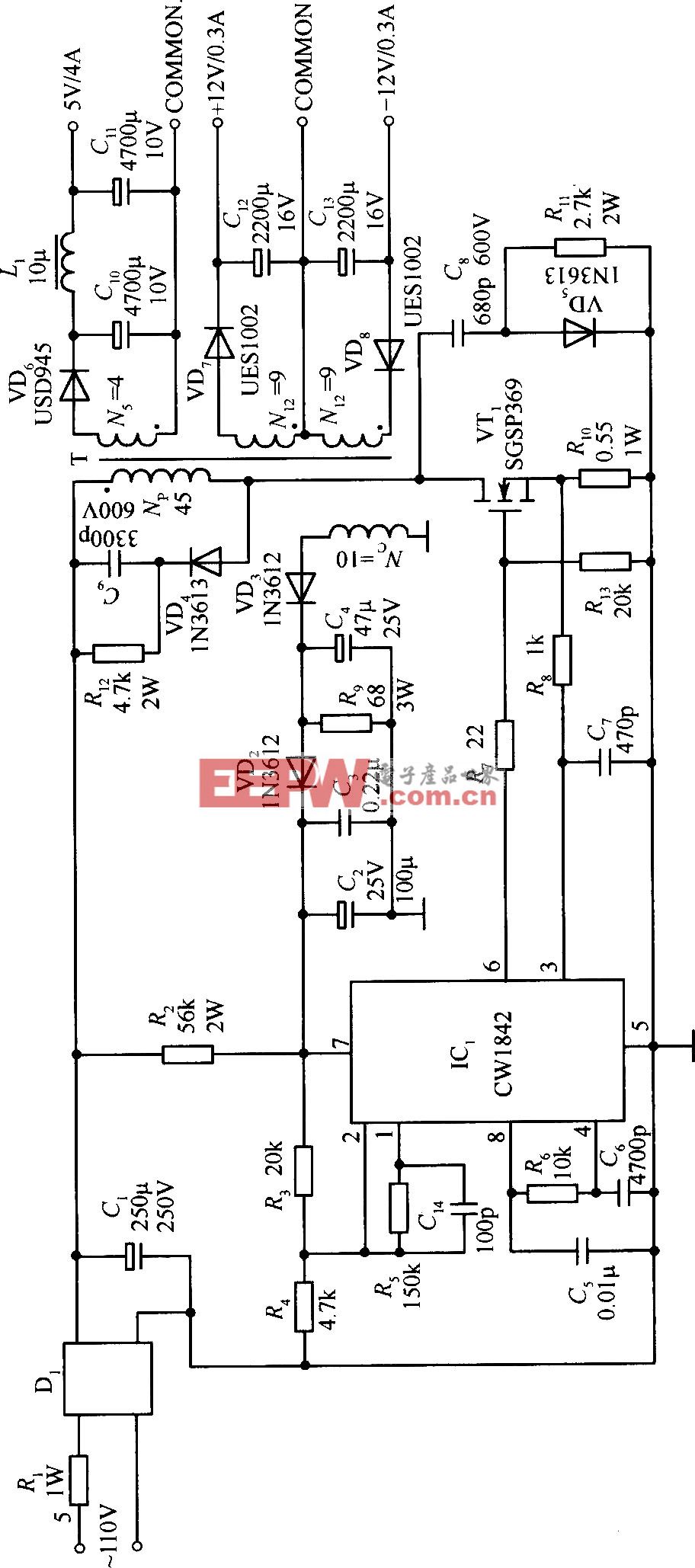

有源箝位DC/DC变换器的电路如图5所示。因电路中使用了有源器件MOSFET(V4)做箝位管,故称之为有源箝位电路。CC为箝位电容,V3为主功率开关管。由图5可知,当V4导通时因uGS3=0而使V3关断。当V4关断时uGS3使V3导通,就对由变压器漏感产生的尖峰电压起到了箝位作用。

图6

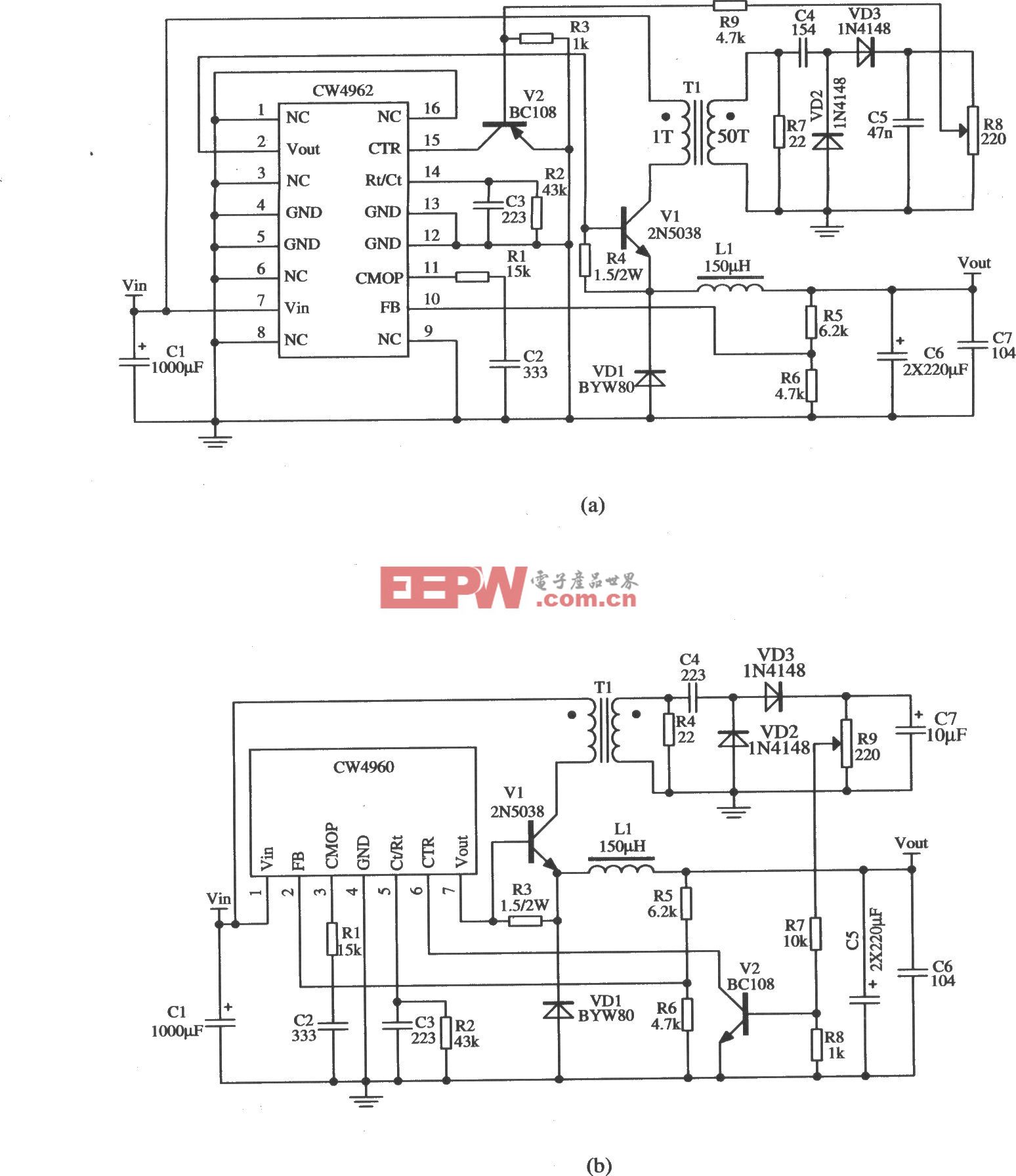

3 16.5W同步整流式DC/DC电源变换器的设计

下面介绍一种正激、隔离式16.5WDC/DC电源变换器,它采用DPA-Switch系列单片开关式稳压器DPA424R,直流输入电压范围是36~75V,输出电压为3.3V,输出电流为5A,输出功率为16.5W。采用400kHz同步整流技术,大大降低了整流器的损耗。当直流输入电压为48V时,电源效率η=87%。变换器具有完善的保护功能,包括过电压/欠电压保护,输出过载保护,开环故障检测,过热保护,自动重启动功能、能限制峰值电流和峰值电压以避免输出过冲。

由DPA424R构成的16.5W同步整流式DC/DC电源变换器的电路如图6所示。与分立元器件构成的电源变换器相比,可大大简化电路设计。由C1、L1和C2构成输入端的电磁干扰(EMI)滤波器,可滤除由电网引入的电磁干扰。R1用来设定欠电压值(UUV)及过电压值(UOV),取R1=619kΩ时,UUV=619kΩ50μA+2.35V=33.3V,UOV=619kΩ135μA+2.5V=86.0V。当输入电压过高时R1还能线性地减小最大占空比,防止磁饱和。R3为极限电流设定电阻,取R3=11.1kΩ时,所设定的漏极极限电流I′LIMIT=0.6ILIMIT=0.62.50A=1.5A。电路中的稳压管VDZ1(SMBJ150)对漏极电压起箝位作用,能确保高频变压器磁复位。

功率MOSFET与双极型晶体管不同,它的栅极电容CGS较大,在导通之前首先要对CGS进行充电,仅当CGS上的电压超过栅-源开启电压〔UGS(th)〕时,MOSFET才开始导通。对SI4800而言,UGS(th)≥0.8V。为了保证MOSFET导通,用来对CGS充电的UGS要比额定值高一些,而且等效栅极电容也比CGS高出许多倍。

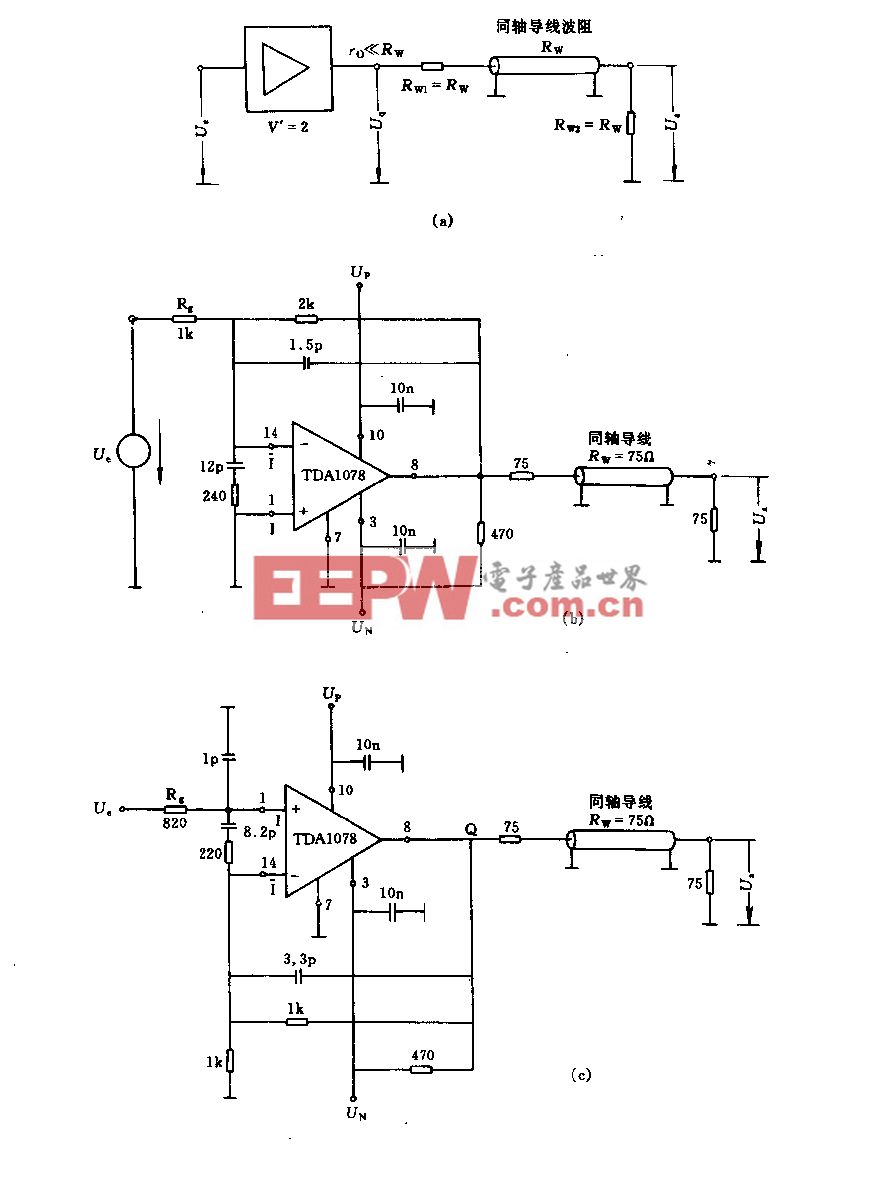

SI4800的栅-源电压(UGS)与总栅极电荷(QG)的关系曲线如图7所示。由图7可知

QG=QGS+QGD+QOD (1)

式中:QGS为栅-源极电荷;

QGD为栅-漏极电荷,亦称米勒(Miller)电容上的电荷;

QOD为米勒电容充满后的过充电荷。

当UGS=5V时,QGS=2.7nC,QGD=5nC,QOD=4.1nC,代入式(1)中不难算出,总栅极电荷QG=11.8nC。

等效栅极电容CEI等于总栅极电荷除以栅-源电压,即

CEI=QG/UGS (2)

将QG=11.8nC及UGS=5V代入式(2)中,可计算出等效栅极电容CEI=2.36nF。需要指出,等效栅极电容远大于实际的栅极电容(即CEI?CGS),因此,应按CEI来计算在规定时间内导通所需要的栅极峰值驱动电流IG(PK)。IG(PK)等于总栅极电荷除以导通时间,即

IG=QG/tON (3)

将QG=11.8nC,tON=13ns代入式(3)中,可计算出导通时所需的IG(PK)=0.91A。

同步整流管V2由次级电压来驱动,R2为V2的栅极负载。同步续流管V1直接由高频变压器的复位电压来驱动,并且仅在V2截止时V1才工作。当肖特基二极管VD2截止时,有一部分能量存储在共模扼流圈L2上。当高频变压器完成复位时,VD2续流导通,L2中的电能就通过VD2继续给负载供电,维持输出电压不变。辅助绕组的输出经过VD1和C4整流滤波后,给光耦合器中的接收管提供偏置电压。C5为控制端的旁路电容。上电启动和自动重启动的时间由C6决定。

输出电压经过R10和R11分压后,与可调式精密并联稳压器LM431中的2.50V基准电压进行比较,产生误差电压,再通过光耦合器PC357去控制DPA424R的占空比,对输出电压进行调节。R7、VD3和C3构成软启动电路,可避免在刚接通电源时输出电压发生过冲现象。刚上电时,由于C3两端的电压不能突变,使得LM431不工作。随着整流滤波器输出电压的升高并通过R7给C3充电,C3上的电压不断升高,LM431才转入正常工作状态。在软启动过程中,输出电压是缓慢升高的,最终达到3.3V的稳定值。

4 结语

在设计低电压、大电流输出的DC/DC变换器时,采用同步整流技术能显著提高电源效率。在驱动较大功率的同步整流器时,要求栅极峰值驱动电流IG(PK)≥1A时,还可采用CMOS高速功率MOSFET驱动器,例如Microchip公司开发的TC4426A~TC4428A。

评论