基于可编程计数器的时序逻辑电路设计

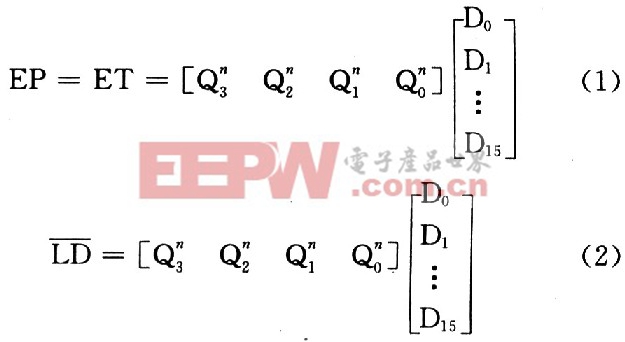

74LS161可编程计数器处于不同现态时通过数据选择器选择不同的外部输入信号作用于EP,ET及

74LS161可编程计数器的EP,ET及

如果所实现的时序逻辑电路其状态个数不超过8个,可使用74LSl61可编程计数器的低3位和2个8选1数据选择器进行组合。

如果所实现的时序逻辑电路其状态个数不超过4个,可使用74LSl61可编程计数器的低2位和2个4选1数据选择器进行组合。

由状态转换关系,依表2确定式(1),式(2)中输入矩阵的参数。

1.3 时序逻辑电路的输出函数

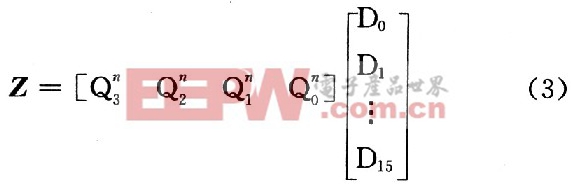

所设计的时序逻辑电路为Mealy型时,输出是现态及输入变量的函数,可写成式(3)所示的矩阵形式并用数据选择器实现,由各状态的输出要求确定式(3)中输入矩阵的参数。

所设计的时序逻辑电路为Moore型时,输出仅是现态的函数:

用卡诺图化简求出最简输出逻辑表达式,用逻辑门实现。

当每态对应一个不同的输出函数时,可用二进制译码器实现输出函数。

1.4 基于可编程计数器时序逻辑电路的设计

一般设计步骤:

(1)作出状态图

使用MSI可编程计数器及数据选择器设计时序逻辑电路时,状态的简化通常不会简化电路结构,一般不进行状态简化,直接使用原始状态图进行设计,可使各个状态所表示的含义清楚,电路与所实现的逻辑功能之间的对应关系较为明确。

(2)状态分配

进行状态分配时,尽量使用不需进行预置数的二进制时序,尽量对非二进制时序作相邻分配,以利于预置数的简化。

(3)求出EP,ET及

(4)画出逻辑图。

2 设计举例

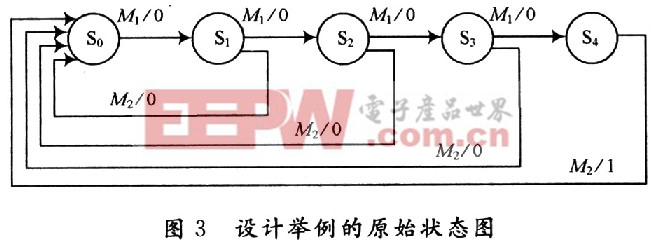

一个同步时序逻辑电路,输入信号为M1,M2。当M1连续输入4个或4个以上的1时,然后M2输入1个1时,输出Z为1,M1,M2不同时输入1。本文引用地址:http://www.eepw.com.cn/article/180632.htm

由设计要求作出原始状态图如图3所示。其中,S0状态表示起始;S1状态表示M1输入了1个1;S2状态表示M1输入了2个1;S3状态表示M1输入了3个1;S4状态表示M1输入了4个或4个以上的1。

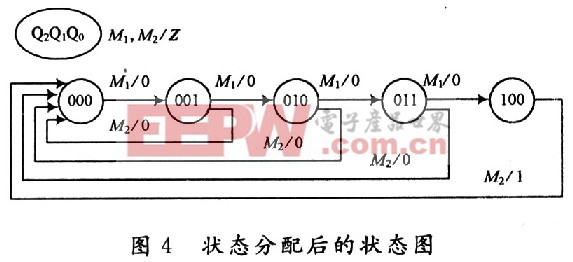

图3中有S0~S4共5个状态,使用74LSl61可编程计数器的低3位代码进行状态分配,按尽量使用二进制时序的分配原则,状态分配关系为:S0:000;S1:001;S2:010;S3:011;S4:100。

状态分配后的状态图如图4所示。

评论