基于FPGA的LVDS内核设计及其外围电路设计

2.2 FPGA设计本文引用地址:http://www.eepw.com.cn/article/177585.htm

FPGA的设计中,发送及接收FIFO的设计用了双口快内存(Block RAM),时钟倍频器用了延迟锁定环(DLL)。帧解码器由30位并行数据产生器、同步字检测阵列和接收状态机组成。以下重点介绍帧编码器和串化器的设计。

(1)帧编码器的VHDL语言设计

帧编码器包括一个长为256的计数器和一个四状态的单热点状态机,用以产生同步帧和数据帧。部分代码如下:

PROCESS(RESET,CLK) //产生长256的计数器

IF RESET='1'THEN COUNT=0;

ELSIF CLK'EVENT AND CLK='1' THEN COUNT=(COUNT+1)MOD 256;

END PROCESS;

TC='1'WHEN COUNT=255 ELSE '0';

TYPE STATE_TYPE IS(IDLE,PACK1,PACK2,TRANSMIT);

SIGANL SREG:SETAT_TYPE;

RPOCESS(CLK,RESET) //状态机进程

IF CLK'EVENT AND CLK='1'THEN

IF RESET=1 TEHE SREG=IDLE ELSE

CASE SREG IS

WHEN IDLE=>

IF SEND_UD='1'THEN SREG=TRANSMIT; //空闲状态如有发送命令,即转入发送状态

ELSE SREG=PACK1; //否则,发送填充字1

WHEN PACK1=>

(后略)

(2)串化器的原理设计

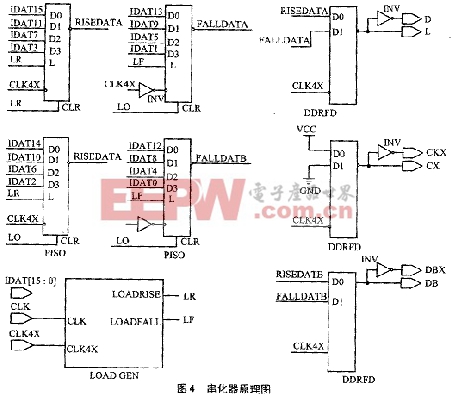

串化器由多级嵌套的子图和若干宏模块组成,原理图的顶层图如图4所示。四个四位并入串出寄存器将16位并行数据拆分为四组串行数据,其中的奇数位和偶数位分别通过一个双数据速率寄存器,得到两个差分信号,同时用另一个双数据速率寄存器产生与之同步的差分时钟。其中,双数据速率寄存器为时序敏感器件,其内部主要部分都加入了时序特性限制,如最大时滞(maxdelay)、最大抖动(maxskew),并用FMAP控件强制性地把相关信号放入同一个函数产生器中。

图4 串化器原理图

3 硬件设计要点

①BLVDS信号的偏置电压为1.25V,电压摆幅只有350mV,传输速率≥100Mb/s;因此,电路板制作至关重要,要求至少使用四层板。

②为使干扰信号只以供模方式加到差分线对上(不影响数据正确性),要求差分线对间的距离尽可能小。BLVDS标准要求差分阻抗为100Ω

给出。其中,ZDIF为差分线对的差分阻抗,εR为印制板介电常数,δ为信号层到电源层的厚度,b为导线宽度。本电路选用的线距及线宽均为0.18mm。

③考虑到阻抗不匹配引起的信号反射和导线的电导效应,要求XCV50E芯片的差分引脚尽可能地靠近子卡的边缘连接器(≤1.52cm),并给每个差分引脚串联一个20Ω的贴片电阻。

④电源方面:Virtex芯片上电时要求有大于500mA的驱动电流,同时,由于多个输出引脚的电位快速变化,要求每对电源和地引脚都要良好旁路。公式:

4 结论

当使用40MHz的外部时钟时,BLVDS总线上的传输速率为120Mb/s,成功实现了多个通信子卡间的高速数据通信。现在,我们正将该通信系统移植到我单位与胜利油田联合研制的SL-6000型高分辨率综合测井系统上。

评论