A/D转换器THS1206在红外成像系统中的应用

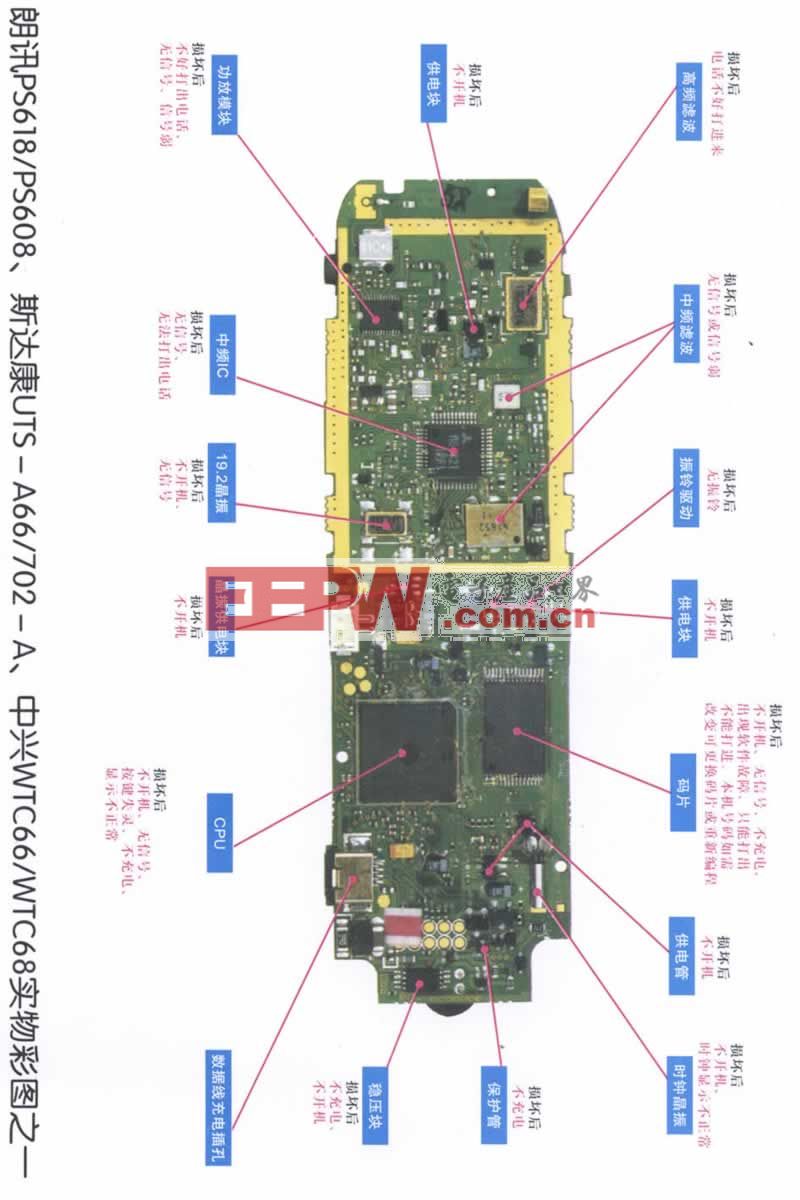

其主要的控制寄存器说明如下:

①VREF:参考电压选择,0为内部参考电压,1为外部参考电压;

②MODE:模式选择,0为连续转换模式,1为单独转换模式;

③CHSEL0、CHSEL1、DIFF0、DIF1:通道和差分模式选择;

④OVFL/FRST:FIFO溢出标志位或FIFO复位控制;

⑤TRIG0、TRIG1:环形FIFO深度设置;

⑥DATA_T、DATA_P:中断信号DATA极性控制;

⑦RBACK:控制寄存器参数回读使能位。

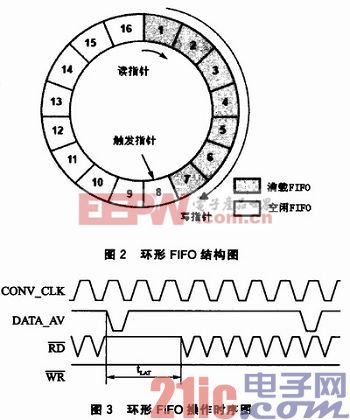

1.3 环形FIFO

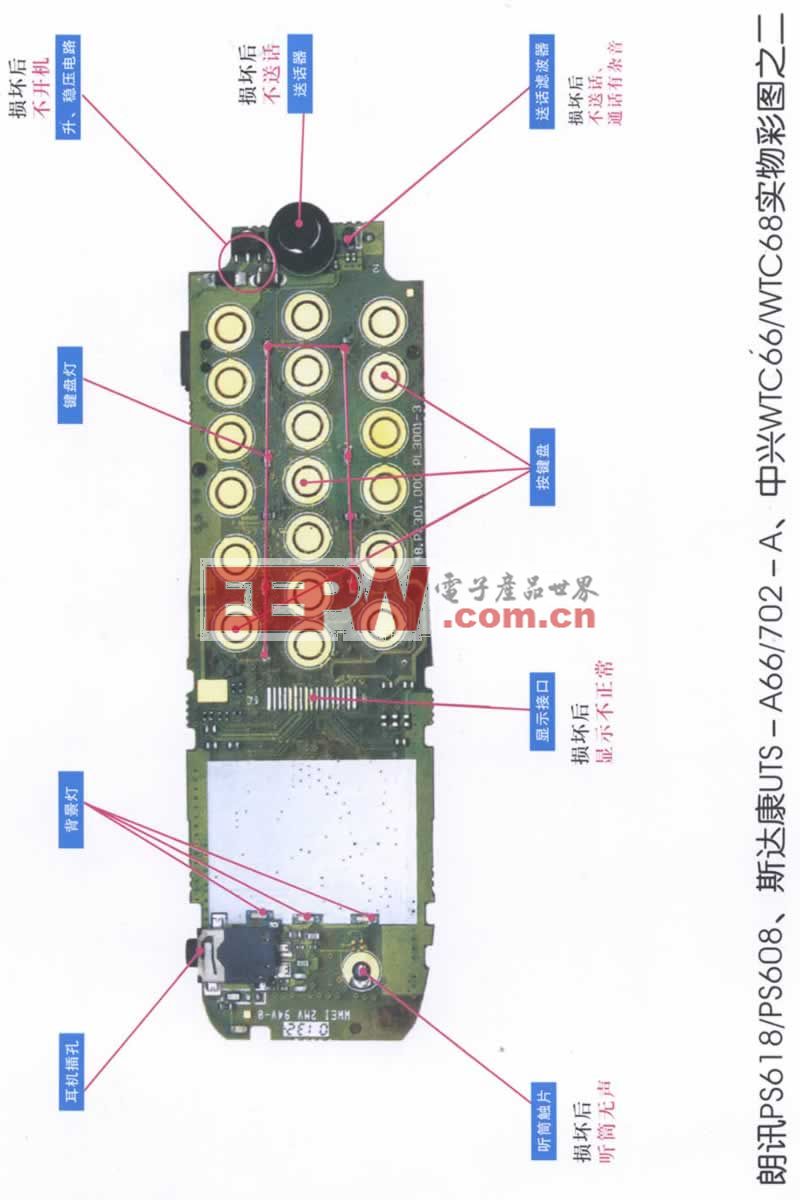

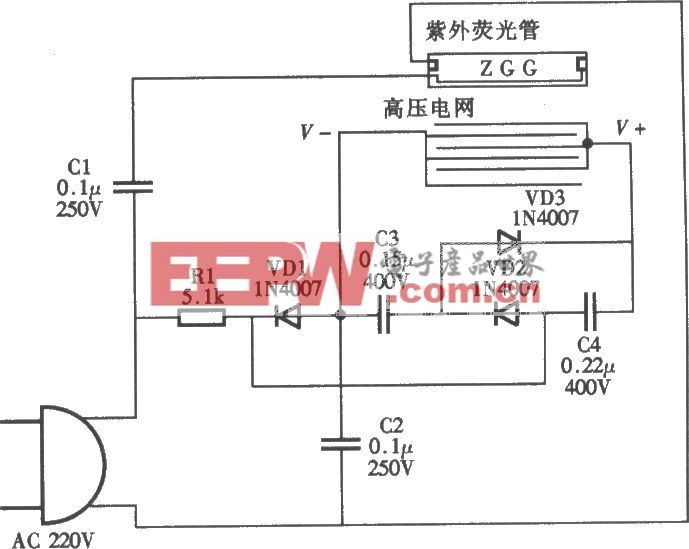

THS1206内部集成一个12位,最大深度为16的环形FIFO,用于实现与处理器的高速数据链接。该FIFO为一个可编程环形存储器,可以缓存内部转换后的数据,允许数据的写溢出。环形FIFO的结构图如图2所示。本文引用地址:http://www.eepw.com.cn/article/175982.htm

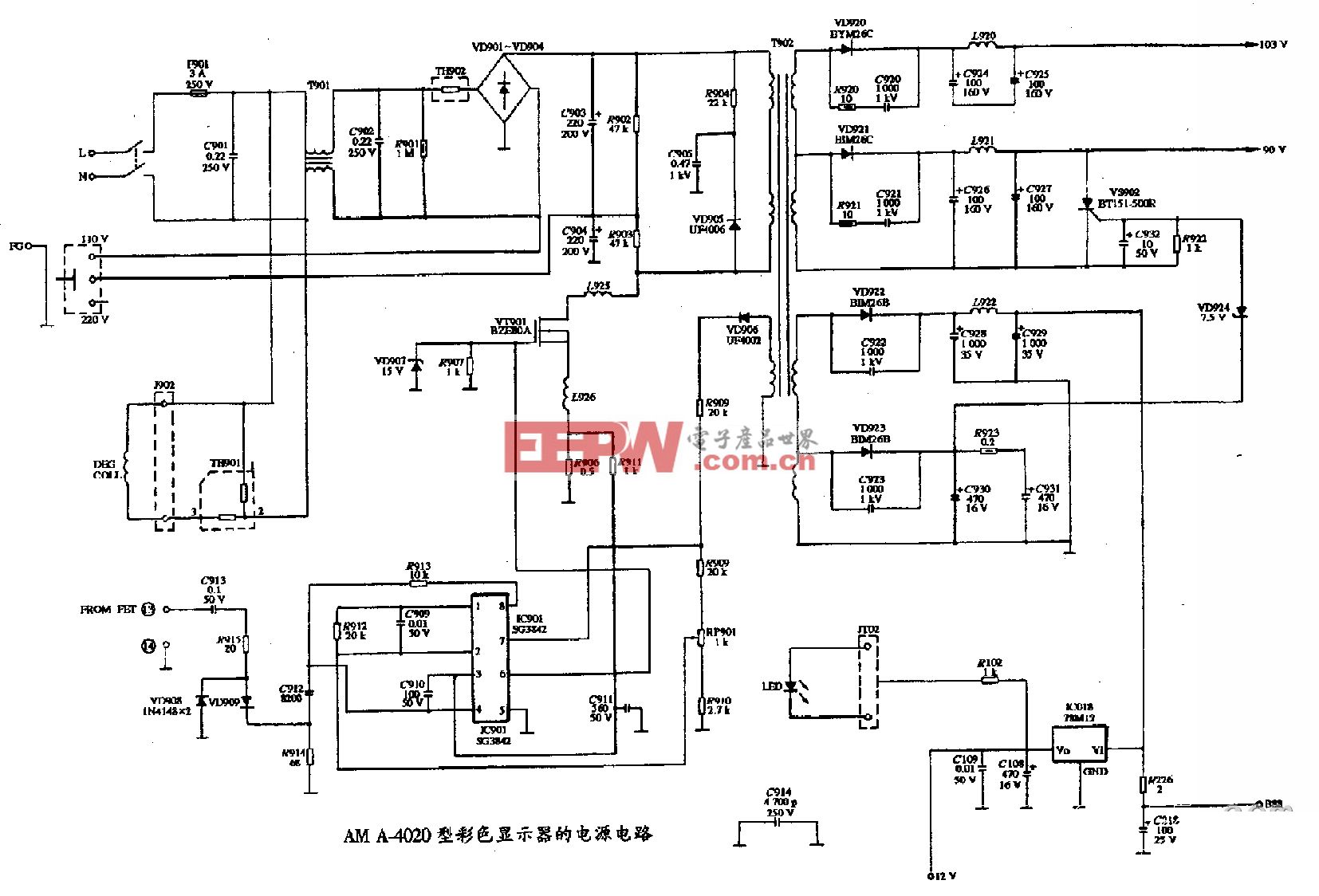

数据根据芯片采集通道设置的不同,自动将数据按顺序写入FIFO中;读、写和触发指针控制了数据的写入和读出过程。首先,通过控制寄存器,设置FIFO的写入深度;当FIFO内数据到达写入深度后,中断信号DATA_AV有效,此时外部控制器需要及时将数据读出。需要注意的是,在实际设计中,经常会因为读写时序关系,导致数据采集失败。时序如图3所示。

该设计采样时钟CONV_CLK为6 MHz,触发深度为8。由于系统设计原因(例如PCB走线延时、处理器内部路径延时等),触发信号有效到开始读出数据迟滞的时间较长(tLAT),致使FIFO数据尚未完全读出时,处理器又向FIFO中写入新的数据,结果数据溢出,数据采集系统不能正确采集数据。因此,在设计中,应保证在中断信号有效时,将FIFO中数据及时读出。

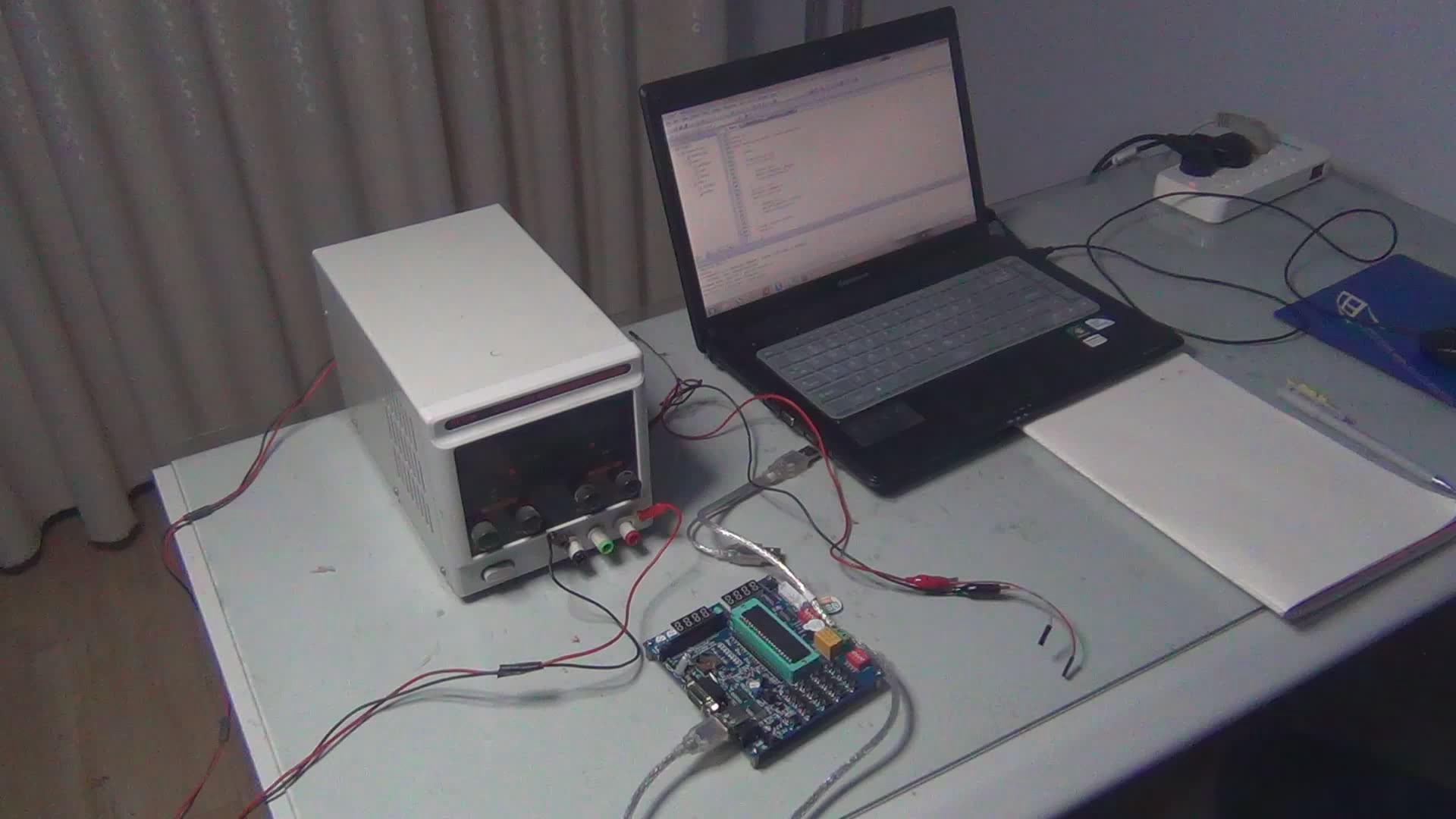

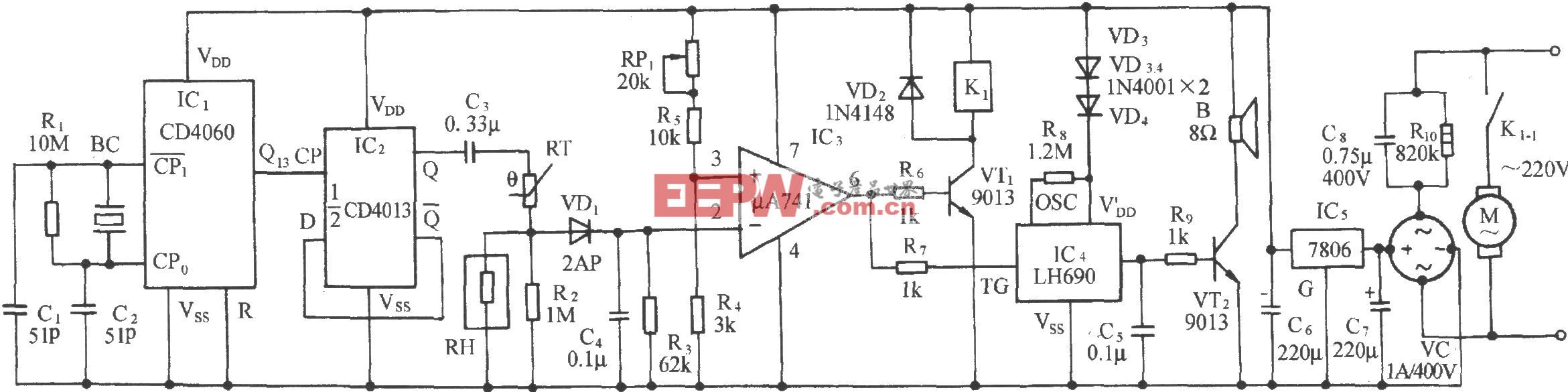

2 红外成像系统

该红外成像系统由光敏感器、FPGA逻辑单元、主控单元和A/D转换单元组成。功能原理图如图4所示。

光敏感器选用Indigo公司的基于碲铬汞结构的ISC0002系列红外面阵探测器。该探测器像元分辨率为640×512,像元尺寸25μm×25μm,最大输出像元速率10 MHz。该探测器分两路输出图像数据,数据率为2 MHz,可将各转换后的像元图像信息电压输出。FPGA逻辑单元选用Xil inx公司的FPGA芯片XCV300,该芯片包含30万门逻辑资源,为光敏感器提供驱动时序,并与主控制器通信,实现各控制功能;A/D转换单元使用了一片THS1206,将红外探测器的两路模拟图像信号转换为数字信号,返回FPGA逻辑单元;最后,FPGA逻辑单元将数据打包整合,输出至图像快视设备,显示图像。

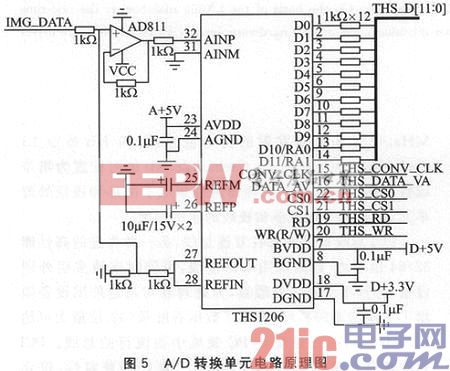

3 THS1206硬件设计

THS1206可以方便地和FPGA等处理器进行无缝连接。图5为红外成像系统A/D转换单元电路原理图。

评论