谈谈电源去耦

这一讲,我们先就大家对电源设计中的去耦问题的疑问作统一的解答,希望看过之后能对你能有所帮助!

本文引用地址:https://www.eepw.com.cn/article/175206.htm谈到DC-DC转换 (及抗噪),探讨的问题一般涉及各种器件,如采用各种系统结构的线性稳压器和开关稳压器 (我们以前已经讨论过了)。设计工程师必须注意这些器件的性能特性,如负载和线路调整、电噪声、开关噪声、输入与输出驱动、有效功率以及热量管理。但就所有这些设计问题的核心而言,DC-DC转换最基本的定义就是通过零输出阻抗和无噪声电路,将DC电压转换为另一种DC电压 (即使是相同电压) ! 。如果您设计的每一种集成电路中,每个电源引脚连接无噪声、0 Ω 输出阻抗DC-DC转换器,电路不会出现电源导致性能下降的现象,达到极为出色的效果。因此,必须了解能够达到这样性能水平的无本底噪声DC-DC转换器!

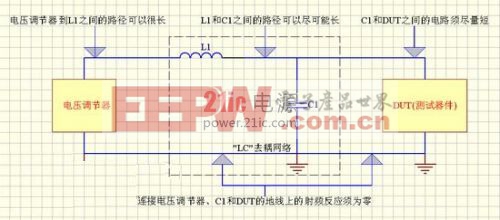

图1. “LC” DC-DC转换器去耦网络

如图1所示“LC”网络。这是一种带噪声抑制功能的最基本DC-DC转换器。简单来说,在尽可能靠近加电器件处放置一支电容C1,将其连接“LC”网络输入电源的同一地线,即可构成理想的0 Ω输出阻抗无噪声DC-DC转换器。其基本原理是去耦概念。

去耦的意思是将电路的一部分与另一部分断开。一个带电器件 (DUT) 产生的噪声可以通过串联元件 (如电感器 (L1)) 与稳压器分开,然后通过电容 (C1) 等并联元件接地。例如,当需要调整 DUT 电压时,改变 DUT 电压显而易见电流也会发生变化。稳压器必须适应电流的变化,尽可能减小电压变化。如果稳压器不能对 DUT 所需电量立即做出响应,DUT 电压也会发生变化,造成系统性能严重下降。

“LC”网络在这方面发挥极为重要的作用。去耦电容 C1可以用作DUT的本地能源。电容不能提供总DC电量,因为它仅保存了少量能量,但这种能量可以极快的速度对DUT的AC电流变化做出响应。电容有效维持本地电源电压,频率可由kHz至GHz (毫秒到纳秒)。电感器用来隔离稳压器与DUT。电感器 DC (和低频) 阻抗应为0 Ω,高频应为高阻抗。这种高频高阻抗可在电容通过器件引脚为DUT提供本地电源时,避免稳压器为DUT提供高频电源。电感器还可以构成LC滤波电路,降低加电状态下稳压器对DUT的输出噪声,同时还可以滤除DUT产生的噪声,防止破坏稳压器输出 (以及稳压器输出连接的其他电路)。DC完全透明,彼此之间以及每条带电电路与稳压器输出安全隔离是去耦的最低要求!

下面来看实际“LC”网络。我们知道,电感器的电抗是XL=ωL,电容的电抗XC=1/ωC。DC处,电感器的电抗 (ωL) 理想状态下为零,但随着频率上升,可提高到无穷大 (理想状态下)。这种情况与电容正好相反。DC处,随着频率上升,电容的电抗 (1/ωC) 下降,并且在理想状态下保持无穷大。当然,在特定频率处,这两个电抗相等,但符号相反。处于这种情况时的频率称为谐振频率f。因此:

将角频率转换为Hz,我们得到

式中,f代表谐振频率。

现在,我们举例说明如何采用通用器件构成“LC”网络。如果DUT电源脚处C1=.1uF,L1 选择2.5 uH,采用现成的VK-200型铁氧体磁芯电感,谐振频率约为318 kHz。这个“LC”网络可以带限稳压器的输出噪声,同时带限DUT返回给稳压器输出的噪声,从而将特定DUT与稳压器“去耦”,防止电路中的另一DUT受到破坏。

下一讲,我们将介绍电路设计和电路板布局中如何采用“LC”网络去耦,以及如何设计各种应用中的电感器。同时,一定要注意电路设计正确去耦,请记住,无论设计数字电路,还是模拟电路,由于速度越来越快,最好一切从模拟而不是数字开始!

评论