基于FPGA的8位并行输入LED扫描控制芯片设计

设计中考虑到帧频与LED屏体显示效率的折中,采用λ=l,td=h/16,即存储器读出速率等于数据输人速率,显示基本时间单位为1/16倍行周期。灰度扫描通过对灰度数据按位分时显示的方法实现,即计算机屏幕图像以每像素24bit输出(红、绿、蓝各8bit)时,通过给每种颜色sbit字节的不同位分配不同的显示时间达到灰度显示的目的。比如,最低位(第8位)对应1/16行显示时间,第7位对应1/8行显示时间,…,第2位对应4行显示时间,最高位对应8行显示时间。屏体数据更新时间以行周期为单位,最低位对应更新时间为1行时间,其中显示1/l6行时间,其余15/16行时间里,由控制电路产生消隐信号进行消隐,其余位类同。

2、LED扫描控制芯片

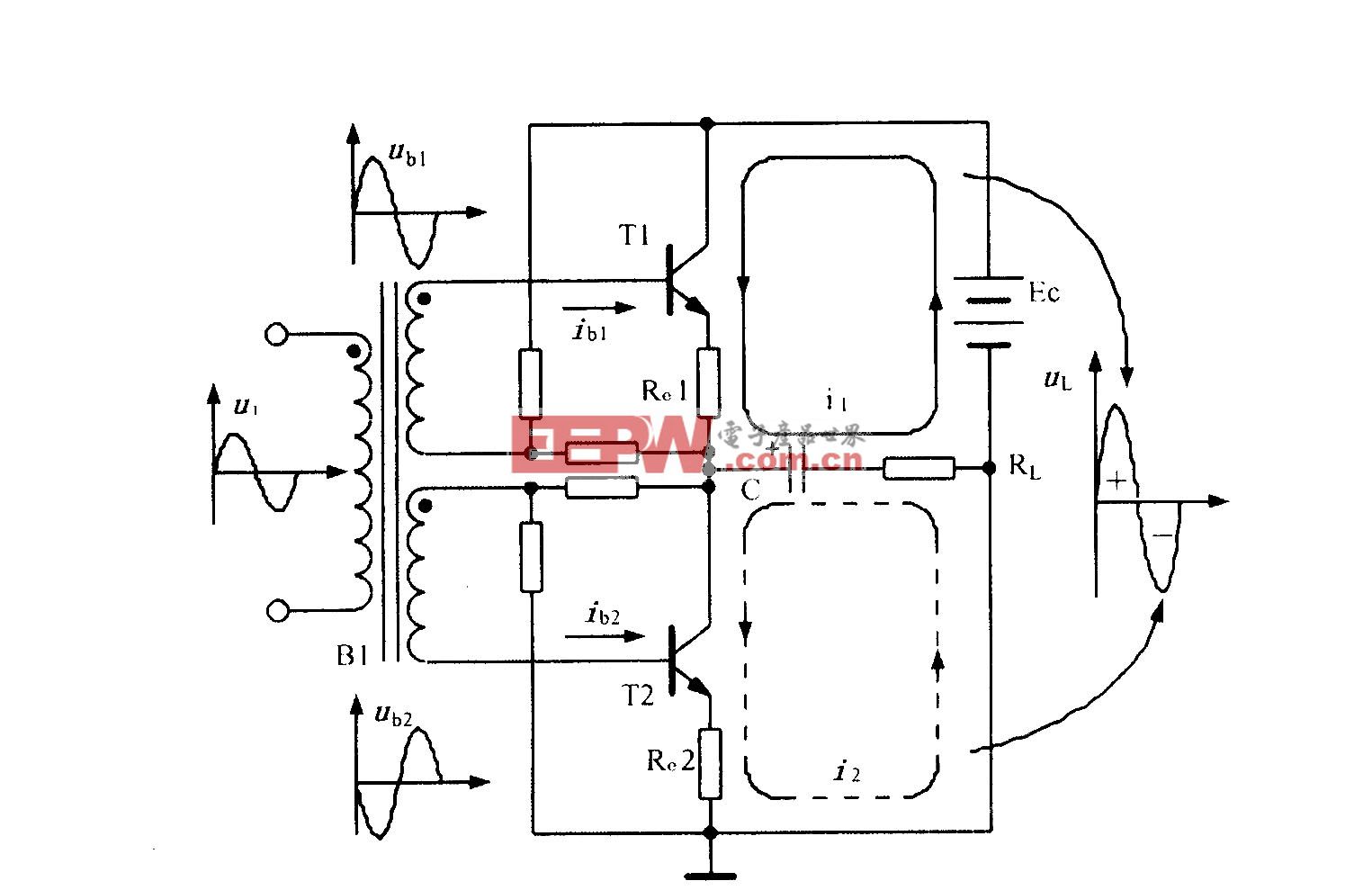

通过数据比较之后,本论文采用了恒流源驱动方式[4],设计了一款可以实现从白到黑的256级灰度显示的控制单元。该显示控制芯片具有与时钟同步的8位并行输入端口,内含16个8位的移位寄存器和16个8位的数据锁存器,可以对8位并行数据进行移位并锁存。图2为该扫描和显示控制芯片的电路图。本文引用地址:http://www.eepw.com.cn/article/169517.htm

当电路开始工作时,8位并行数据在移位时钟脉冲的作用下打入芯片的移位寄存器模块中,其内部含有16个移位寄存器, 故移位16 次后,数据将从该芯片的DOUT0~DOUT7 输出到下一芯片;同时将移位所得的16个8位数据输入到锁存器中锁存。这时只要输出控制信号为低,并给出同名行的行选通信号同时使输出开放,各列即可开始输出恒流,同时8位计数器开始对灰度级时钟进行计数,当计数值与该列所存储的灰度值相等时,该列的恒流输出结束,从而实现相应LED的显示时间控制,即占空比控制。若采用10个该显示控制单元级联驱动LED显示屏,则一直并行移位160 次就可完成第一行数据的传输。

运用VerilogHDL编写代码并用Modelsim仿真软件对该电路代码进行编译仿真,得出了如图3、图4所示得时序图。

通过时序图我们可以看到在控制端:enable、rsel、bc_ena、latch等控制端的控制下,可以按照不同的需求来实现对不同灰度和亮度的实现。在灰度控制单元中,数据在经过了16个脉冲之后移位传输至输出端输出,并且实现了8列或者16列输出的可调;在亮度控制单元中,通过调整enable、bc_ena、latch的值实现了输出数据的可调,从而准确的实现了亮度的控制功能。

根据各部分同名行的全部传输时间等于该同名行的显示时间, 可以得到行周期和点(列)周期的值,即行周期=帧周期/扫描方式的行数,点周期=行周期/(每行点数×部分数)。若帧频为120Hz ,则帧周期为1/120s = 8.33ms,根据扫描方式为1/16可将80行分为5个16行,每行160 列,这样,行周期即为520.6μs;点周期为650.75ns;点频为1.54×106Hz。

四、结论

本文讨论了LED大屏幕视频控制器中的灰度扫描方法,本文提出了256灰度级扫描时的实现方案,作者的创新点在于并设计了一款从暗到亮的256级灰度显示的LED显示控制芯片,在本设计中帧频可达120Hz ,行周期为520.6μs,点周期为650.75ns;点频为1.54×106Hz。该芯片可以通过多块级联来驱动LED大屏幕,有着较好的应用前景。

评论