易修改无需处理器干预的LED灯序电路设计

LED技术越来越多的应用到我们的生活中,对于开发者来说,通过片上系统(SOC)平台实现LED或其他设备次序器,从而找到一种减少成本、降低设计难度的设计需求变得越来越普遍。SOC器件通过单芯片集成了完整LED子系统所需的单片机功能和各种数字外围设备。本文介绍了一种基于最新SOC技术的简单的8 LED灯序电路设计。在这个设计中最精彩的部分就是微处理器无需进行干预。不是采用传统的由单片机处理器干预的被动的数字外设,此设计完全是基于SOC数字系统的智能分布式处理功能。这使中央处理器从管理灯序电路的工作中解脱出来,节省CPU资源从而设计效率更高。

本文引用地址:http://www.eepw.com.cn/article/169021.htm该设计方法可以很容易的扩展到LED以外的需要用指定顺序开启或关闭的其他设备,比如不同长度、不同模式的序列定时器等等。该设计示例中还有额外的功能:

· 7位计数器(TC)终端计数

· 指示设备开启关闭的输出

· 为序列器件提供的8位输出

· 给Verilog状态机的时钟输入

· 给8位ALU(bit-slice)处理器的总线时钟

这篇文章中用到的开发工具是赛普拉斯半导体可编程片上系统(PSoC)的集成开发环境PSoC Creator。

原理图设计

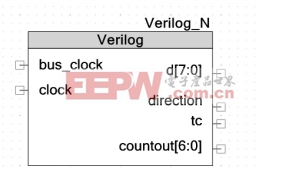

设计的第一步是在创建一个Verilog符号来定义输入、输出和与之相关的位宽度(见图1)。一旦上层Verilog模型(原理图)已经建立,它就可以用来产生包含所有模块中引脚定义的Verilog源文件。这一步不需要开发功能Verilog代码。

图1:Verilog 符号。

刚才创建的Verilog符号现在可以放置到高层原理图设计。在这里,每一个输入及输出都能连接到时钟源、I / O引脚、状态和控制寄存器等等。8-LED灯序电路高层原理设计见图2。

图2:高层原理设计示例。

评论