分享:探索白光LED劣化原因

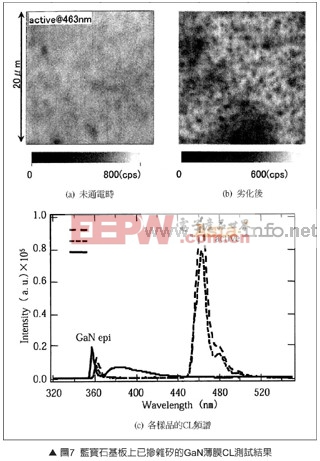

根据图7(a)、(b)可知劣化组件,强度降低的暗带有增加趋势,换句话说暗带会随着施加电压,贯穿转位与V型瑕疵数量明显增加,结晶性降低则造成无辐射迁移的机率增加,最后导致强度降低。若仔细观察图7(c)的频谱,严重劣化组件的CL频谱,463nm活性层产生的发光光线几乎完全没有发现。除此之外研究人员还针对日本新能源与产业综合技术开发机构(NEDO;New Energy and Industrial Technology Development Organization)提案的“利用近场的次世代阴极发光法(CL;Cathodo Luminescence)与拉曼(Raman)分光仪计划,开发利用近场光的“阴极发光法”与“拉曼分光仪”。

该计划还应用紫外共鸣拉曼效应与特殊形状的探针,开发紫外雷射光激发近场共鸣拉曼分光仪,全球首度成功以100nm以下空间分辨率评鉴硅的应力,目前研究人员正检讨应用在化合物半导体的评鉴。有关InGaN的量子井结构,使用上述新开发的阴极发光法分光仪,能够超越传统阴极发光法100nm的空间分辨率极限,以10nm的空间分辨率,检测InGaN的量子井结构内部「V-defect」周围的成分变化。

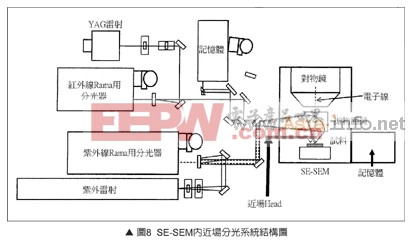

上述计划主要目的是提升阴极发光法的分辨率,为缩小电子束的直径,研究人员采用新型萧基发射式 (SE;Schottky Emission) 电子j,制作高分辨率扫描式电子显微镜 (SE-SEM;High-Resolution Schottky Emission-Scanning Electron Microscope)。

分光系统组合椭圆镜与光纤,扫描电子线的同时进行阴极发光法频谱检测,它采用与传统分光系统不同的新型分光系统。新型分光系统使用厚6mm、焦距2mm超小型抛物面镜,驱动压电平台(Piezo stage) 利用非扫描电子线方式取得阴极发光的频谱。换句话说试料释放的阴极发光,在抛物面镜集光后再利用检测器检测,由于它只检测一点释放的阴极发光,因此上述新开发设备的分辨率,比组合椭圆镜、光纤的分光系统大幅提升。

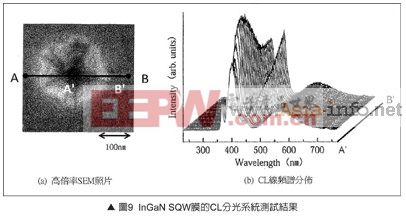

透过椭圆镜的使用,高分辨率扫描式电子显微镜除了阴极发光的检测之外,还能够检测拉曼频谱与光致发光(Photoluminescence)。图8是上述新开发高分辨率扫描式电子显微镜内近场分光系统的结构图。接着研究人员使用新开发的阴极发光分光系统,检测GaN 2μm/蓝宝石上制成的InGaN单量子井结构 (SQW;Single Quantum Well) 膜层,亦即In0.02Ga0.98N7nm/In0.20Ga0.80N3nm/In0.20Ga0.98N7nm的阴极发光频谱,值得一提是上述膜层是典型蓝光LED常用成分而且InGaN的单量子井结构膜层,具备对组件良品率与耐久性重大影响的 V-defect。

图9(a)是V-defect的高倍率扫描型电子显微镜影像;图9(b)是5nm步进检测时,V-defect附近阴极发光线频谱分布的检测结果,图9(b)的阴极发光线频谱分布检测,主要是沿着图9(a)扫描型电子显微镜影像线A-B进行。图9(a)观测到的波长364nm与448nm发光线,被归类成各缓冲层的GaN与InGaN量子井层之间的发光。此外560nm附近观测到的宽阔发光线,主要是黄色瑕疵的缓冲层GaN缺陷造成的发光线。由于V-defect的斜面可以观测到波长400nm的发光线,因此研究人员认为该发光线反映V-defect斜面InGaN单量子井结构的In成分变化。

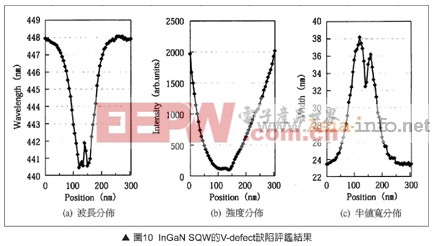

图10是448nm附近InGaN单量子井结构膜层产生的发光线峰值波长、强度、半值宽度评鉴结果。由图10(a)可知越靠近V-defect底部,峰值波长越往短波长端移动,而且In的成分越少,反过来说在V-defect的底部,峰值波长移动到长波长端,这代表V-defect的底部In的成分非常丰厚。

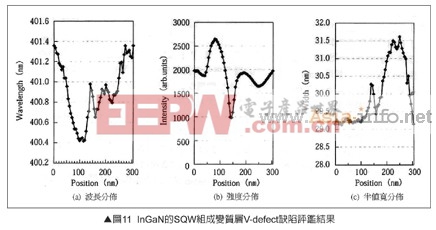

图11是400nm附近InGaN单量子井结构膜层,产生的发光线峰值波长、强度、半值宽度评鉴结果,由图11(a)可知V-defect的斜面强度变强,成分的变质主要集中在V-defect的斜面。

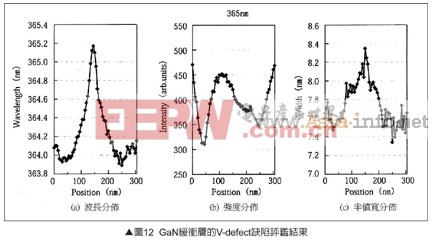

图12是GaN缓冲层(2μm)的发光线峰值波长、强度、半值宽度评鉴结果,由图12(a)可知峰值位置先移动到短波长端,越接近V-defect的底部越移动到长波长端,波长移动到长波长端主要是In扩散到GaN层所造成。至于移动到短波长端就无法以In成分变化作说明,特别是近V-defect附近的峰值波长变化,主要是硅组件内部硅局部氧化部位,发生类似应力变化所致。

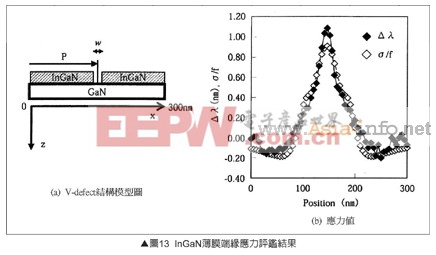

图13是以w的空间将V-defect近似化,接着根据GaN膜层上以w的间隔堆栈的InGaN薄膜的结构,计算InGaN薄膜端缘产生的应力,其结果如图13(b)所示,图中黑色菱形是实测数据,白色菱形是计算数据,由图可知实测结果与计算结果两者非常一致。

根据上述资料,研究人员针对V-defect的形成机制提出以下发生模式,分别是:(1)为缓和InGaN单量子井结构膜层与GaN积层界面的应力,In会扩散到GaN膜层内部使贯穿转位稳定化。(2)持续使InGaN单量子井结构膜层成长时,为掩埋贯穿转位InGaN单量子井结构膜层内部的In量缺损,此时会出现InGaN单量子井结构膜层的成分变质层。(3)InGaN单量子井结构膜层继续成长,为确保InGaN单量子井结构膜层内部成分变质层的In,In量缺损的InGaN单量子井结构膜层必须继续成长,因此InGaN单量子井结构膜层的成分变质层厚度会增加,其结果造成400nm附近成分变质层产生的发光线强度增强,最后形成所谓的“V-defect”。换句话说LED芯片的劣化,主要是贯穿转位与V-defect增生所造成。

结语

以上介绍利用过电压劣化试验的分析结果。有关白光LED芯片的劣化,主要原因是缺陷增生造成,除此之外树脂与荧光体的劣化也必须列入考虑。目前国外业者正进行白光LED灯泡的温度加速试验,分成光劣化与热劣化两大类别,详细分析荧光体的劣化机制,一般认为随着劣化机制的掌握,未来对提升白光LED的寿命有正面帮助。

评论