LED大屏幕控制电路设计方案研究

摘要:在综合分析LED大屏幕显示系统设计中控制电路的诸多设计方案的基础上,分别给出了以单片机、可编程逻辑器件和嵌入式计算机技术为控制核心的不同设计方案的实现方法,对这几种方案的特点进行了比较,并介绍了应用情况。

本文引用地址:https://www.eepw.com.cn/article/167981.htmLED点阵是公共信息的一种重要显示终端,其中大屏幕LED点阵显示屏在许多场合得以应用。大屏幕显示技术比中小屏幕显示难度更大,因为其屏幕大,LED点数多,而又要在极短时间内刷新每个点,这就要求其扫描速率必须非常高,此外,大屏幕作为信息发布的重要媒介,对其稳定性、可靠性以及可扩展性要求都很高,只有设计合理的控制电路才能满足上述要求。本文着重讨论LED大屏幕设计中控制电路的几种设计方法,针对不同的设计要求给出了不同的解决方案。

1LED大屏幕系统的工作原理

典型的LED大屏幕显示系统主要由信号控制系统p扫描和驱动电路以及LED阵列组成,系统结构如图1所示。目前大多数LED显示屏的屏幕设计采用的是模块化的结构,它的基本单元是LED显示单元模块,屏幕大小和形状可灵活改变,显示屏的安装和维护也十分方便。

图1系统原理框图

信号控制系统是微机系统p单片机系统p微机Z单片机主从控制系统p可编程逻辑器件控制系统、红外遥控系统p传呼接收与控制系统等等。信号控制系统的任务是生成或接收LED显示所需的数字信号,并控制整个LED显示系统的各个部件按一定的分工和时序协调工作。行驱动电路多为三极管阵列,给LED提供大电流。列驱动由串入并出移位寄存器和锁存器(或带锁存功能的移位寄存器)构成。

待显示数据就绪后,控制系统首先将第一行数据送入移位寄存器并锁存,然后由行扫描电路选通LED阵列的第一行,点亮一段时间后,再以同样方法显示后续行,直至完成一帧的显示内容,如此循环往复。根据视觉暂留的原理,能够实现24f/s的显示才能够让肉眼没有明显的停顿感,相当于响应时间要达到,40ms以下。当LED显示屏面积很大时,传输的数据量也非常大,从而增加了显示系统的响应时间引起闪烁,为提高视觉效果,可以分区并行显示。

在高速动态显示时,LED的发光亮度与扫描周期内的发光时间成正比,所以通过调制LED的发光时间与扫描周期的比值(即占空比)可以实现灰度显示。

2LED大屏幕控制电路的设计

控制电路的设计是大屏幕系统设计的核心,控制电路设计包括信号控制系统、扫描电路和驱动电路的设计,控制电路的设计一般由数据存储器、数据缓存器、计数器p同步控制器p读写控制器p主从控制器、地址控制器、帧存储器p数据选择器、灰度调制器、移位寄存器等构成。目前来说,LED显示屏控制电路设计广泛采用两类器件作为其控制核心来实现,一类是单片机控制系统,另一类是可编程逻辑器件。

2。1基于单片机的控制电路设计方案

基于单片机的控制电路主要有两种方案,一种是一片单片机作为主控器件控制和协调大屏幕整个显示系统的显示,一种是多片单片机构成多处理器,其中一片作为主CPU,其它作为子CPU一起控制大屏幕的显示。

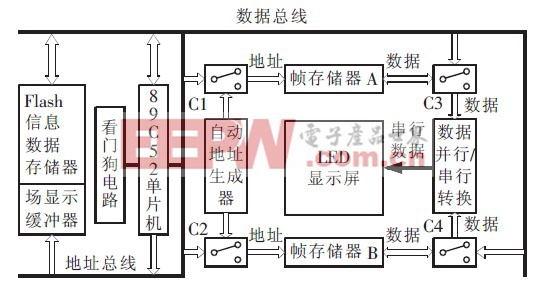

图2是采用单片CPU设计的控制电路机构示意图,用89C52单片机作为控制核心。单片机接收从PC机或其他信息源发送来的显示数据,存储在Flash中,同时用RAM6264作为场显示缓存区,以实现不同显示播出方式。89C52控制切换开关C1,C3和C2,C4同时对帧存储器A,B交替进行数据的读写操作,将读出的数据进行并行5串行转换送给显示屏进行显示刷新。其中,自动地址生成器由4个计数器串联构成,并配以振荡电路提供计数时钟,对于一个M×N个像素的单色屏,当刷新频率为60Hz时,计数频率为M×N×60Hz对于多灰度级彩色大屏幕,数据送到显示屏之前要进行灰度调制重现图像的色彩,对数据的处理速度要求更高,采用单片机控制可能在速度上无法满足要求。

图2单片CPU控制电路结构示意图

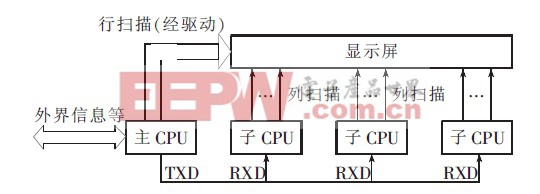

由于目前很多单片机的I/O口具备了15mA以上的驱动能力且价格比较便宜,因此在大屏幕的设计中也采用多处理器方案。系统的基本特点是:一个显示组中有多个处理器,包括一个主CPU和多个子CPU,其结构示意图如图3所示。主CPU的任务是通过数据采集或与外界通信等获取显示信息,再传输给子CPU,主CPU还负责行扫描和发送显示同步信息等。子CPU接收主CPU的数据信息并存放到内部RAM。中,再根据主CPU发出的控制信息选择适当的列输出口进行列扫描。假设每个子CPU可用作输出口的最多引脚数为m,而每块LED矩阵的列数为n,则每块芯片所能驱动的LED块最大数为m/n这样,每个单片机负责一块或几块>LED块,灵活性强,便于扩展,同时减轻了主CPU的负担,提高了点阵的刷新频率。

图3多CPU控制电路结构示意图

在多画面显示的大屏幕设计中,这种方案较为理想,对不同的显示画面采用单独的子CPU进行列扫描,再通过主CPU进行统一的行扫描,虽然控制电路使用的元件较多,但电路结构简单,易于实现。

2。2基于CPLD/FPGA的控制电路设计方案

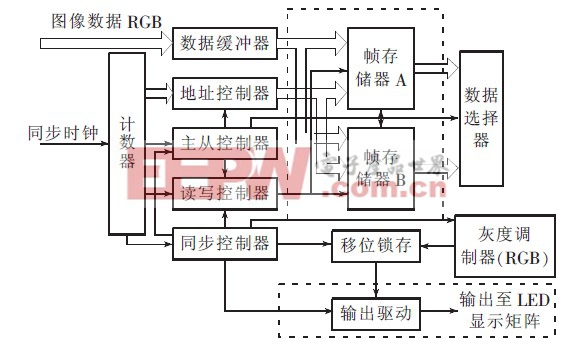

频图像信号频率高:数据量大,要求实时处理,加之LED大屏幕电路的数字逻辑相当复杂,采用CPLD/FPGA设计控制电路,可以简化系统结构,便于调试。图4是CPLD/FPGA设计控制电路的原理图。采用CPLD/FPGA器件对其中的同步控制、主从控制、读写控制和灰度调制等大量电路进行了集成,使图像数据处理更为快速,图像更加稳定,而且系统结构紧凑,工作可靠性有所提高。

图4CPLD/FPGA控制电路原理图

图4中虚线以外的其它功能模块均有CPLD/FPGA编程实现,将复杂的硬件电路设计通过软件编程来取代。与图2的单片机控制电路对比来看,电路结构明显更简洁,电路的面积减小及可靠性增强,调试也更为简单,由于CPLD/FPGA可以并行处理多个进程,比起单片机对任务的顺序处理效率更高,点阵的刷新频率也随之提高。

评论