基于ISD1420的高响度语音电路设计

介绍一种语音电路的设计,说明了设计原理及控制方法。该环节利用语音存储/再生芯片ISD1420、BTL功率放大电路及扬声器构成大功率语音电路,由单片机根据主控PLC的命令进行发声控制。

关键词:语音存储/再生芯片;BTL电路;单片机

Design of a High Volume Voice Circuit Based on ISD1420

LI Ping, LI Yarong, GUAN Tianmin

(Dalian Jiaotong University, Dalian 116028, China)

Key words: voice record/playback chip; BTL circuit; singlechipcomputer

1系统构成

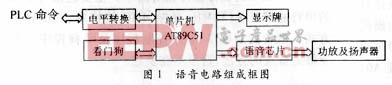

语音电路组成框图如图1所示。由PLC发布RS232电平信号,经电平转换后,为单片机AT89C51所接收。一方面控制语音芯片ISD1420放音,同时控制高亮度数码显示牌给出倒计时信号,为被训练人员提供提示。看门狗则保证该电路正常运行。

语音电路组成框图如图1所示。由PLC发布RS232电平信号,经电平转换后,为单片机AT89C51所接收。一方面控制语音芯片ISD1420放音,同时控制高亮度数码显示牌给出倒计时信号,为被训练人员提供提示。看门狗则保证该电路正常运行。

2.1语音电路构成

根据训练要求,语音电路在起跑前10秒发出“长提示音”一声,然后每隔一秒发“短提示音”一声,计时回零时发“发令枪声”(发声规律可调)。

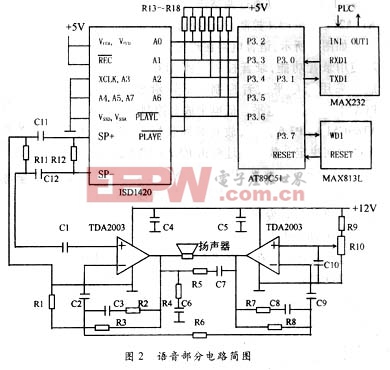

语音部分电路设计见图2。“提示音”与“起跑枪声”由语音存储/再生芯片ISD1420分段存储,ISD1420输出的音频信号经电容耦合到两片集成功率放大器TDA2003构成的BTL功放电路,最后由扬声器输出。MAX232将PLC送过来的RS232电平信号转换成TTL电平并送到单片机AT89C51,AT89C51根据PLC的指令,通过P3.6控制ISD1420的放音,P3.2~P3.5用来调整放音地址。MAX813L则作为看门狗为单片机AT89C51提供上电复位和运行监控,由P3.7提供喂狗信号。

根据训练要求,语音电路在起跑前10秒发出“长提示音”一声,然后每隔一秒发“短提示音”一声,计时回零时发“发令枪声”(发声规律可调)。

语音部分电路设计见图2。“提示音”与“起跑枪声”由语音存储/再生芯片ISD1420分段存储,ISD1420输出的音频信号经电容耦合到两片集成功率放大器TDA2003构成的BTL功放电路,最后由扬声器输出。MAX232将PLC送过来的RS232电平信号转换成TTL电平并送到单片机AT89C51,AT89C51根据PLC的指令,通过P3.6控制ISD1420的放音,P3.2~P3.5用来调整放音地址。MAX813L则作为看门狗为单片机AT89C51提供上电复位和运行监控,由P3.7提供喂狗信号。

选用语音存储/再生芯片ISD1420。该电路采用EEPROM存储方法将模拟语音数据直接写入半导体存储单元中,具有音质自然、可反复录放、抗干扰、低功耗等许多优点。ISD1420放音时间为20秒;最多可分为160段,每段段长最少125ms;输入采样6.4kHz;100000次录音周期;5V单电源供电,放音电流15mA,维持电流0.5μA。完全满足设计需要。使用28引脚的DIP封装芯片,引脚功能见参考文献[5]。

地址引脚(A0~A7)有两个作用,取决于A7、A6的状态。当A7或A6有一个为“0”时,A0~A7解释为地址位,作为当前录放操作的起始地址。我们设计的电路使用了A0~A7的地址位功能。ISD1420的地址空间分配见表1。

地址引脚(A0~A7)有两个作用,取决于A7、A6的状态。当A7或A6有一个为“0”时,A0~A7解释为地址位,作为当前录放操作的起始地址。我们设计的电路使用了A0~A7的地址位功能。ISD1420的地址空间分配见表1。

评论