基于AD9516的宽带高动态数字中频系统采样时钟设计与应用

摘 要:数字中频系统中高速ADC、DAC 对采样时钟有着很高的要求,对此设计了一种新的基于AD9516 的CDMA2000 数字中频系统采样时钟合成方案。本文在提出该数字中频系统硬件方案的基础上,介绍了AD9516 芯片及其在本系统中的具体应用,给出了MCU 与AD9516 数据通信方式和芯片主要寄存器配置内容,且详细分析了时钟相位噪声和时钟抖动的测试方法。最终在对基于此时钟方案制作出来的数字中频系统PCB 板仔细调试之后,测试了时钟相噪与抖动以及整个系统SNR ,整体指标达到设计要求。

本文引用地址:http://www.eepw.com.cn/article/162382.htm随着3G 牌照的发放,在3G 网络建设的初期,直放站是移动通信网络优化的重要设备,而直放站核心部分数字中频技术在现代通信系统中具良好的应用前景。但数字中频系统主要部分ADC、DAC对采样时钟的要求很高,其在很大程度上决定了系统的整体性能。本文就该数字中频方案所要求的采样时钟,设计了基于AD9516 的时钟合成方案。与同类方案如某款芯片加外置VCO 比较,该方案在设计灵活性、芯片功能特性、电路简单、成本低等方面均有很大的优势。文中介绍了AD9516 芯片特性,着重说明了其在本方案中的具体应用,以及此处MCU 如何以FPGA 为桥梁与AD9516 芯片进行数据配置,还分析了时钟相位噪声与抖动对SNR 的影响,最后对制作出来的PCB 板进行了时钟相噪与抖动以及系统SNR 的测试,结果证明该方案有很好的应用价值。

1 数字中频系统整体硬件框图介绍

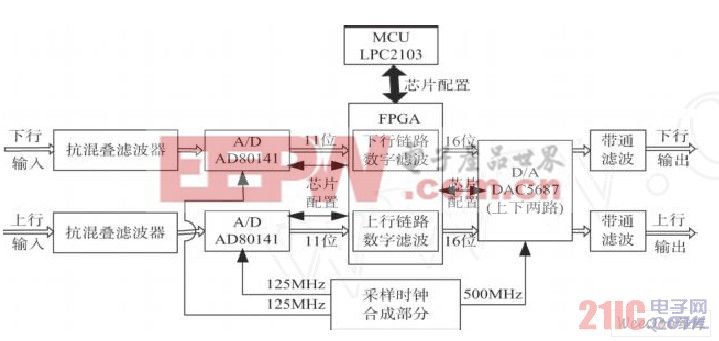

本数字中频系统射频模拟输入信号中心频率为162 MHz ,10 MHz 带宽的CDMA2000 信号,系统上下链路前后端均有衰减器对信号进行动态增益控制,该衰减器工作由FPGA 程序实行在线操作实现。硬件电路设计时系统要求选用高性能的ADC、FPGA、DAC 芯片,整个PCB 板由上下两路射频电路,时钟部分,MCU 部分,以及电源组成,电路板上各个芯片的数据读写由ARM 单片机LPC2103 通过FPGA 控制。

具体电路框图及各部分芯片选用如图1 所示:

图1 整体硬件电路设计框图

由于ADC、DAC 芯片都为高精度的数模转换芯片,对时钟的相噪和抖动有很高的要求,故必须选择性能优异的时钟合成芯片。根据所定的信号处理方案,时钟合成单元需提供三路时钟输出作为上下两路的ADC、DAC 的采样时钟。其中上下路ADC芯片为11 bit 、140 MSimple/ s 采样速率的AD80141 各一片,需两路125 MHz 时钟;DAC 芯片为双通道16 bit 、最高可达500 MSimple/ s 采样速率的DAC5687 ,上下路共用一片,故只需一路500MHz 时钟。

2 频率合成单元设计

基于上述要求,综合考虑提出一种新的基于AD9516 工作于内部VCO 模式的采样时钟合成方案,该方案无论从芯片功能、系统要求、设计的灵活性,还是同类方案成本方面都能很好的满足项目要求。并且在整体中频系统PCB 板布局布线时,会尽量考虑时钟线的信号完整性,优化时钟信号质量,测试结果证明所定方案完全符合要求。

2.1 AD9516 芯片简介

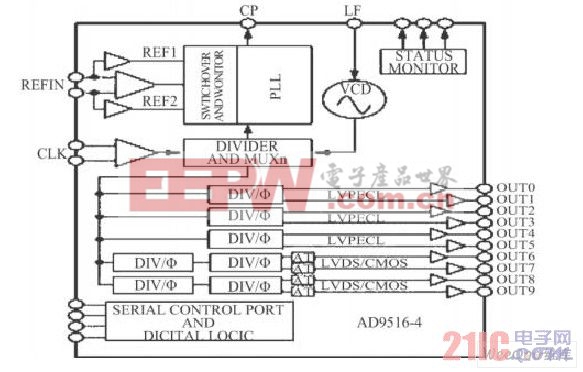

频率合成单元采用AD 公司的AD9516 芯片,它是一款集低相位噪声时钟发生和低抖动14通道时钟分配功能于一体的时钟合成器,其结构图如图2 所示:

图2 AD9516 结构图

评论