基于CY7C68013的高速数据传输系统的设计

摘 要: 采用Cypress公司的CY7C68013芯片设计了通用的USB接口,结合MAX7128的串/并/串转换和光纤收发系统,实现数据的高速传输。介绍了系统的软硬件结构, 详细介绍了固件设计和WDM驱动程序的结构、特性、工作机制、软件流程及与USB设备通信的方法。测试表明,该系统达到了预期的设计目标和实用要求。

本文引用地址:https://www.eepw.com.cn/article/157107.htmUSB控制器是以USB串口引擎为主的专用集成电路,并可延伸至对其进行管理的MCU以及相应的软硬件。目前市场上供应的USB控制器主要有2种:带USB接口的单片机(MCU)或纯粹的USB接口芯片。带USB接口的单片机可分为2类:一类是从底层设计专用于USB控制的单片机,如Cypress公司的CY7C63513、CY7C64013等[1],由于开发工具的专用性,往往应用于各种专业应用场合,如微机主板等[2-4];另一类是增加了USB接口的普通单片机,如Intel公司的8X931、8X930以及Cypress公司的EZ-USB,由于均基于8051内核,因而得到了广泛应用。

1 CY7C68013与系统结构简介

Cypress公司的CY7C68013芯片是集成USB2.0协议的微处理器,支持12 Mb/s的全速传输和480 Mb/s的高速传输,具有控制传输、中断传输、块传输和同步传输4种传输方式,内部包括一个增强型8051处理器内核、一个串行接口引擎(SIE)、一个USB收发器、8.5 KB片上RAM和4 KB FIFO存储器以及一个通用可编程接口(GPIF)。8051可工作在48 MHz/24 MHz/12 MHz时钟频率,内部可自动产生480 MHz的频率供USB2.0串行收发引擎使用。由于数据缓冲器与SIE相连接,数据进入收发器后,通过SIE可直接转向FIFO,通过8 bit或16 bit数据接口与外设连接,存取数据。微控制器不参与数据传输,但允许以FIFO或RAM的方式访问这些共享FIFO,从而实现低速控制、高速传输。CY7C68013有GPIF/SLAVE FIFO/GPIO 3种接口模式,本系统采用Slave FIFO接口模式,选用控制传输和块传输2种方式,外部控制器可像普通FIFO一样对FIFO进行读写。

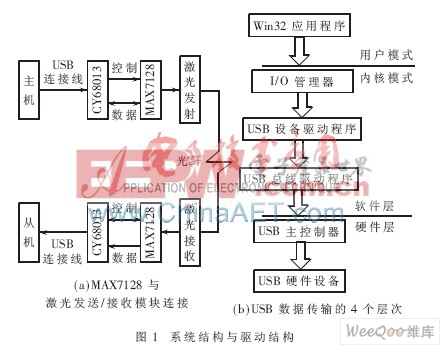

本数据传输系统分为3部分:发送端和接收端、CY7C68013控制器、具有并/串(或串并转换)功能的CPLD芯片(MAX7128)以及光纤传输模块。其中,CY7C68013和MAX7128之间采用并行连接方式,MAX7128与激光发送(接收)模块间是串行连接,如图1(a)所示。

图1(a)中,主机将数据发送到CY7C68013端点FIFO缓冲器中,然后CY7C68013将端点FIFO中的数据分字节放到一组I/O口上,并且使能读信号,MAX7128读取I/O上的逻辑值,当接收512 B后,MAX7128将这512 B的数据从低到高串行发送给激光发送模块;数据经过光纤传输,进入激光接收模块,输出串行信号,通过MAX7128实现串并转换,数据宽度为8 bit,通过CY7C68013的从属FIFO的写入时序即可将数据写入CY7C68013的端点缓冲器中。

USB数据传输接口开发分为4个层次,接口硬件、接口软件、驱动和应用程序如图1(b)所示。

评论