一种64位高速PCI总线接口的设计与实现

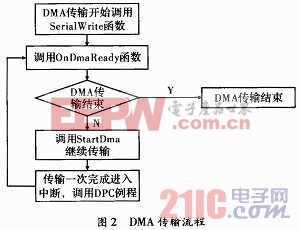

OnDmaReady例程中获取传输的物理内存的地址和字节数,然后设置相应的DMA寄存器值开始DMA传输。DMA传输结束后,应使m_CmxentTm-nsfer无效并删除。具体流程如图2所示。本文引用地址:http://www.eepw.com.cn/article/156552.htm

4 局部总线端设计

本设计中,局部总线端采用了C模式。C模式下可配置3种数据传输方式:单周期方式(Single Cycle Mode)、4字方式(Brust-4 Mode)和连续突发传输方式(Continuous Mode),在本设计中采用了连续突发方式,可以有效地提高输出效率。

PCI9656在局部总线为为主设备,始终占用局部总线,局部总线端的FPGA始终响应PCI9656的操作。方案中使用PCI9656的DMA传输模式,在本地端不需要进行地址译码,因此可以对PCI9656的控制信号进行简化处理,PCI9656的局部端主要控制信号如下

ADS#:一次总线访问开始;

Blast#:总线访问结束;

LW/R#:读写控制信号;

Ready#:从设备准备好信号,有效时表示总线访问进行中;

LHOLD:PCI9656占用本地总线申请信号;

LHOLDA:占用本地总线应答信号;

Wait#:主设备传输暂停信号;

EOT#:数据传输异常中止信号,用于FIFO溢出或空时中断数据传输;

Lint#:用于引起CompaetPCI总线端的中断信号;

LRST#:本地总线复位信号;

CCS#:配置寄存器选择信号。

在DMA传输过程中主要关心的信号可简化为:ADS#、Blast#、LW/R#、Ready#、LHOLD、LHOLDA,如图3所示。

图3中,lclk为本地总线时钟,当PCI9656要发起一次DMA操作时,先发送lhold信号申请本地总线,若本地总线空闲则FPGA发出lholda信号响应PCI9656,然后PCI有效ads_n信号以示总线传输开始,FPGA使ready_n有效以示总线传输正在进行中,此时本地数据通过局部数据线传送到PCI总线,或着数据由PCI总线传送到局部逻辑。一次传输结束时PCI使blast_n信号有效并使lhold信号无效,然后FPGA使lholda信号和ready_n信号无效,一次DMA传输完成。传输中若是DMA读操作则lwr信号拉低,若为写操作则拉高。

本地总线位宽为32位,因此本地总线理论速度为264MB·s-1,由于应用程序的效率问题和传输中一些无效状态的存在,目前PCI总线平均速率达到212 MB·s-1,可以满足目前高速数据采集、传输对总线传输速度的要求。

PCI9656本地总线时序设计中需要注意blast_n信号有效说明为突发传输最后一个时钟周期,此时ready_n信号仍然为有效,否则会造成总线等待;在正常读写访问中CCS#信号应置高,否则总线访问将指向配置空间而非内存或I/O空间。

5 结束语

利用PCI9656和FPGA实现了一种高速PCI总线接口,较全面地论述了总线驱动开发和局部时序设计的过程。这种设计提高了总线传输速度,为高速数据采集系统的实现创造了条件。

评论