基于DSP平台的多音平行体制调制端的实现

摘要 以32音并行体制为例,利用DSP平台实现了多音并行体制的调制端,给出了其主要模块的具体实现方法。由于并行体制技术成熟、成本低、高性价比对提高数据传输速率、消除多径衰落有益。

关键词 多音并行体制;调制;傅里叶变换;DSP

短波通信中常采用多音并行和单音串行两种体制来进行高速数据的传输。单音串行体制仅采用一个载波,串行发送数据信号。由于每个码元占据了整个频谱,码元宽度窄,当传输高速数据时,实现复杂,且码间串扰严重。而多音并行体制的主要思想就是把高速串行信道分裂成许多低速的并行信道,以适应短波信道低速传输的特性,在每个子信道上传送一个副载波,采用频分正交调制,用多个副载波并行传输的方法提高速率。并行体制的传输,是采用加宽码元宽度,使其远大于多径时延,消除多径衰落的影响。并行体制技术成熟、成本低,具有较高的性价比。本文以32音体制为例说明短波并行体制调制端的DSP具体实现方法。

1 32音并行体制调制端的设计

本并行体制在音频频带内采用32个正交副载波音,对比特同步数据传送采用正交差分相移键控(QDPSK)调制。

具体设计要求:

(1)在数据输入端口接收不同速率的串行二进制数据:300 b·s-1,600 b·s-1,1 200 b·s-1;

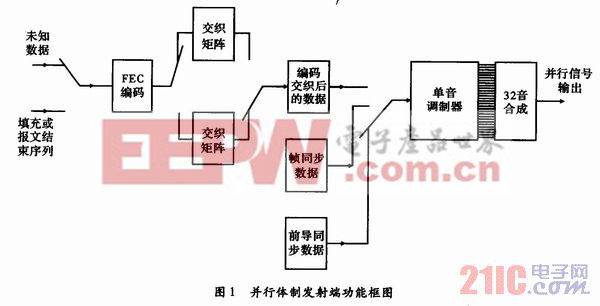

(2)对接收到的二进制数据完成前向纠错(FEC)编码和交织;

(3)每个单音上采用QDPSK调制;

(4)采用32个正交载波音,每个音相隔56.25 Hz;

(5)采用某种分集方式。

图1为多音并行体制下发射端功能框图。

2 软硬件平台介绍

本文实现多音并行调制端的硬件平台如图2所示,主要由计算机PC、DSP-TMS320C6416、A/D芯片TLV320AIC20组成。DSP通过多通道缓冲串口1(McBSP1)与计算机相互通信,同时通过多通道缓冲串口0(McBSPO)与TLV320AIC20相互通信。

本平台采用的TMS320C64xx系列是2000年3月TI正式发布的定点系列,主频1.1 GHz,处理速度接近9 000 MI·s-1总体性能比C62xx提高了10~15倍。

TLV320AIC20是TI公司生产的一款低功耗高性能的双通道A/D芯片,可含有两个16位A/D通道和两个16位D/A通道,完成模拟与数字话音的转换工作,软件可编程寄存器内含有6种可编程的控制寄存器,配置方便。

软件平台采用CCS(Code Composer Studio)系统,其包含一整套用于开发和调试嵌入式应用的工具。它包含适用于每个TI器件系列的编译器、源码编辑器、项目构建环境、调试器、描述器、仿真器以及多种其它功能。

3 并行体制关键模块的具体实现

3.1 核心模块-FFT

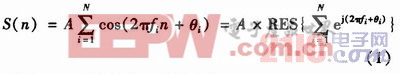

由于发送信号是一组余弦函数的叠加。假设信号是由一组N个频率为f1,f2,f3,…,fN,初始相位为θ1,θ2,θ3,…,θN,幅度为A的余弦信号,故其叠加后的信号为

其中,RES[]是取函数的实部。

从式(1)中可以看出,利用反傅里叶变换(IFFFT)可以方便地产生前导序列和生成调制信号方便。同时反傅里叶变换在DSP中运算量不大,并可以直接调用傅里叶变换,将输入信号的格式稍加处理即可得到反傅里叶变换的结果。

评论